## ПРЕЗЕНТАЦИЯ МИКРОПРОЦЕССОРА

Разработанного в НИИСИ РАН

#### НАЗНАЧЕНИЕ МИКРОСХЕМЫ

- Микросхема цифровой обработки сигналов 1890ВМ7Я с интерфейсом RapidIO представляет собой 128-разрядный микропроцессор с архитектурой SIMD и VLIW.

- Микросхема предназначена для применения в многопроцессорных вычислительных комплексах, ориентированных обработку 32-разрядных вещественных и комплексных чисел одинарной точности, в том числе в системах обработки сигналов, гидроакустике.

#### ТЕХНИЧЕСКИЕ ХАРАКТЕРИСТИКИ

- Тактовая частота 200 МГц

- Пиковая производительность 8 Гфлопс

- Пиковая скорость обмена с памятью ddr2 3,2 ГБайт/с

- Пиковая скорость RapidIO 1 Гбайт/с

- Проектные нормы КМОП 0,18 мкм

- Apхитектура SIMD, VLIW

- Время выполнения задачи сFFT-1024 ~14 мкс

- Напряжения питания 1,8 В; 3,3 В

- Энергопотребление ~8 Вт

- Диапазон рабочих температур от -60 С до +85 С

- Вычисление 4-х бабочек Фурье, 4-х элементарных функций на каждом такте частоты

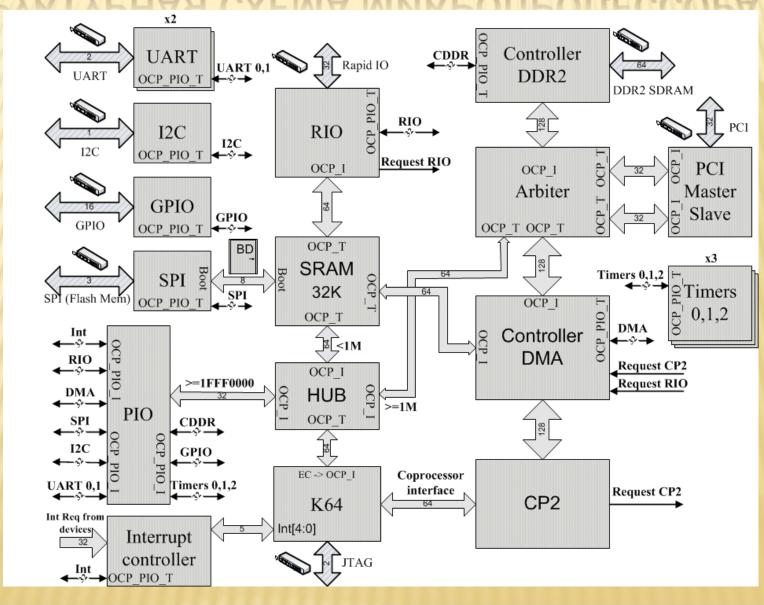

#### СТРУКТУРНАЯ СХЕМА МИКРОПРОЦЕССОРА

### ОРГАНИЗАЦИЯ ВЫЧИСЛЕНИЙ

- Ядро К64 -> Сопроцессор СР2

- Сопроцессор СР2 <->DMA Контроллер

- □ DMA Контроллер <-> RapidIO, ddr2 ram

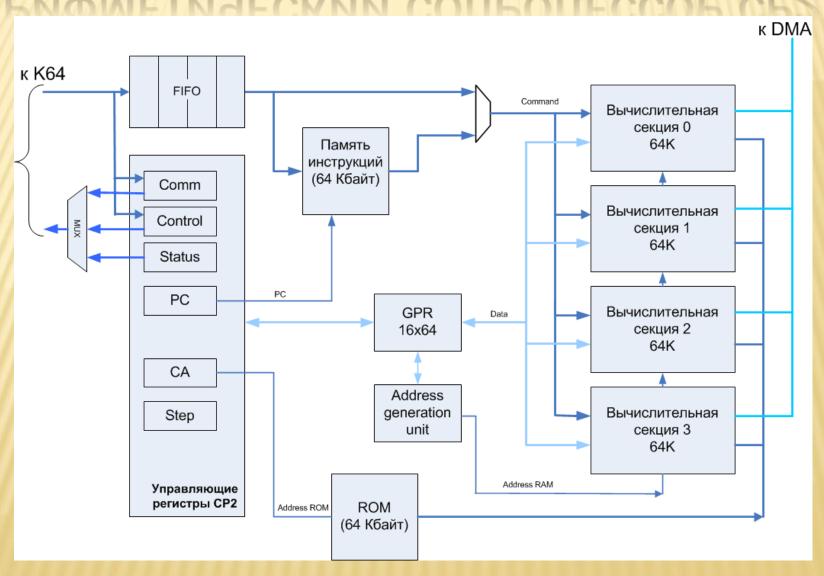

# АРИФМЕТИЧЕСКИЙ СОПРОЦЕССОР СР2

## АРИФМЕТИЧЕСКИЙ СОПРОЦЕССОР СР2

- Apхитектура SIMD:

- 1 поток команд, память команд 64 Кбайт;

- 4 секции, память данных 64 Кбайт в каждой;

- FIFO команд на 8 слов 64разр.;

- 16 GPR регистров и 16 IR интерфейсных регистров 64разр.;

- Адресные регистры AGU:

- 16 регистров адреса 13разр.;

- 16 регистров модификации адреса 13разр.;

- 16 регистров режима модификации 13разр.;

- □ Прямая и косвенная (3 режима) адресация;

- □ Стек подпрограмм (16 ячеек) и стек циклов (16 ячеек);

- ПЗУ коэффициентов для бабочки Фурье 64Кбайт, для углов 0 рі/4;

- □ Отсутствие аппаратной зависимости по данным и ресурсам.

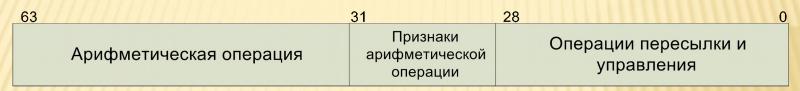

## ОРГАНИЗАЦИЯ КОНВЕЙЕРА КОМАНД

Формат VLIW команды

Арифметический конвейер 9 тактов

Конвейер пересылки данных 4 такта

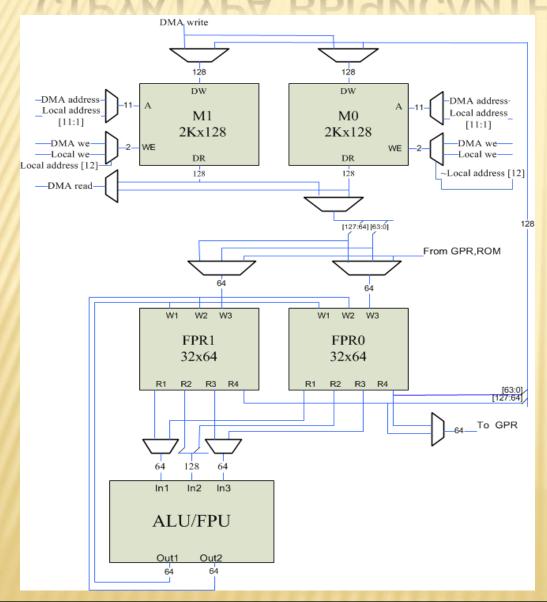

### СТРУКТУРА ВЫЧИСЛИТЕЛЬНОЙ СЕКЦИИ

- ALU:

- 3 входа 64разр.,

- 2 выхода 64разр.;

- 10 операций/такт;

- Регистровый файл:

- 32 регистра 128разр;

- □ 4R/3W;

- □ 03У:

- 4К x 128разр.;

- 2 независимых банка для DMA и ALU;

- Регистры управления ALU.

#### ФОРМАТ ДАННЫХ И СИСТЕМА КОМАНД

- 64-разрядное слово из 2-х 32-разрядных с плавающей точкой одинарной точности:

- □ С комплексное число (32бит–RE, 32бит–IM);

- PS пара вещественных чисел (32бит, 32бит);

- S вещественное число одинарной точности (32 бит);

- PW пара целых чисел (32бит, 32бит);

- W целое число (32 бит).

- Арифметические операции над комплексными числами (Умножение с накоплением, Эрмитово умножение, Бабочка Фурье);

- Арифметические операции над парой 32-разрядных вещественных чисел (Умножение с накоплением, Умножение 2х2-матрицы на вектор, Скалярное произведение 4-векторов);

- Преобразование форматов;

- □ Операции с целыми числами;

- Операции вычисления элементарных функций над 32-разрядными вещественными числами (1/X, 1/rsqrtX, sinX, log2X, 2^X, atanX, приведение аргумента).

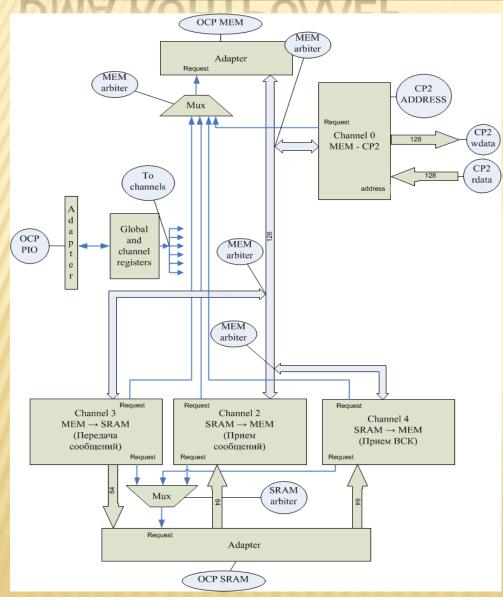

#### DMA KOHTPOMEP

- □ Прием/передача данных DDR2 RAM – CP2 (4 локальных ОЗУ);

- Передача сообщений RapidIO;

- Прием пакетов RapidIO по скоростному каналу;

- Прием сообщений RapidIO.

#### DMA: KAHAA CP2 - DDR2 RAM

- Обмен между ddr2 ram и 4-мя локальными ОЗУ СР2;

- 2 независимых генератора адреса ddr2 и CP2;

- 2-х мерная адресация памятей: Nx, StepX, Ny, StepY, Bx;

- Дополнительные компараторы адреса для каждой из 4-х ОЗУ для разрешения записи данных в СР2;

- 2 режима выгрузки из 4-х ОЗУ СР2: 1) По 1-4 слова из каждого ОЗУ; 2) 4 полных запуска адресного генератора для каждого ОЗУ;

- Бит-реверсивная адресация СР2;

- Синхронизация с СР2;

- Возможность нелинейного (условного) перехода между дескрипторами;

- Нет аппаратной проверки равенства объема данных ddr2 и cp2;

### ИНТЕРФЕЙС RAPIDIO

- Параллельный двунаправленный 8 бит LVDS;

- Частота 250 МГц;

- Пропускная способность в оба направления 500 + 500 Мбайт/сек;

- Прием/отправка пакетов по 256 байт;

- Прием/отправка сообщений (Message) по 4 Кбайт;

- Прием/отправка Doorbell;

- Прием/отправка Maintenance;

#### СРЕДСТВА ОТЛАДКИ И ПРОГРАММИРОВАНИЯ

- □ Компилятор;

- Симулятор (СИ модель);

- E JTAG;

- Операционные системы: Linux, ОСРВ 3.0;

- □ Библиотека VSIPL (~400 функций);

- □ Модули:

- □ 6U 2x 1890ВМ7Я, ddr2 ram, коммутатор RIO, мост RIO, Ethernet, PCI;

- Мезонин 1х 1890ВМ7Я, ddr2 ram, RIO.

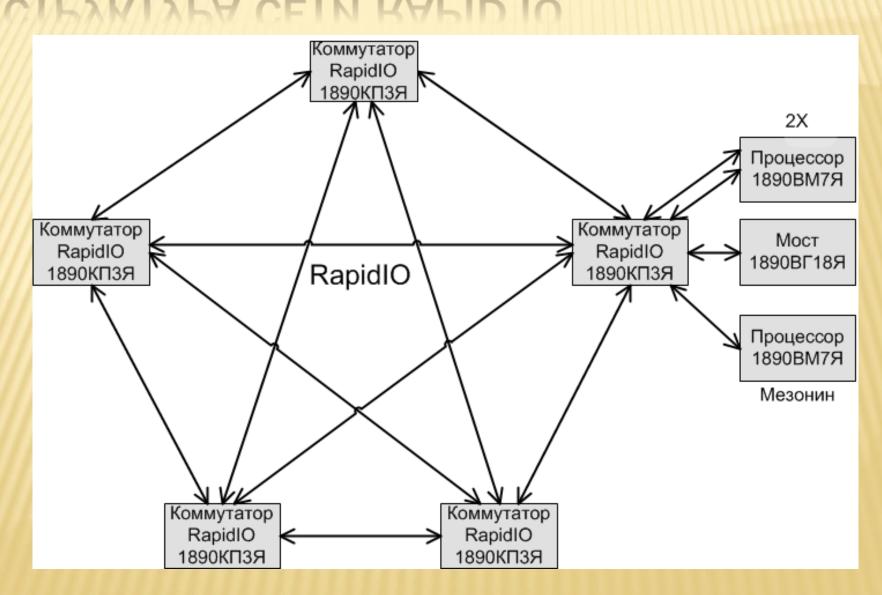

### МИКРОСХЕМЫ С ИНТЕРФЕЙСОМ RAPID 10

- 1890ВМ7Я 128-разрядный специализированный микропроцессор;

- 1890КПЗЯ 8-ми портовый коммутатор параллельного RapidIO;

- □ 1890ВГ18Я мост параллельный/последовательный RapidIO, коммутатор, преобразователь интерфейса от датчиков, контроллер PCI.

## СТРУКТУРА СЕТИ RAPID 10