# FSM-based Digital Design using Verilog HDL

FSM-based Digital Design using Verilog HDL Peter Minns and Ian Elliott © 2008 John Wiley & Sons, Ltd. ISBN: 978-0-470-06070-4

# FSM-based Digital Design using Verilog HDL

Peter Minns Ian Elliott

Northumbria University, UK

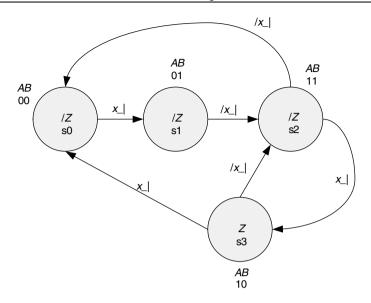

Copyright © 2008 John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England

Telephone (+44) 1243 779777

Email (for orders and customer service enquiries): cs-books@wiley.co.uk Visit our Home Page on www.wileyeurope.com or www.wiley.com

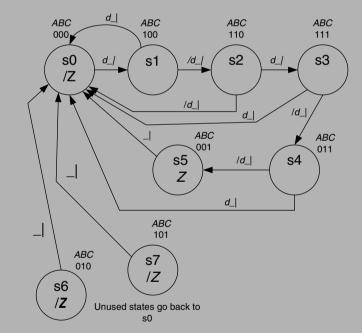

All Rights Reserved. No part of this publication may be reproduced, stored in a retrieval system or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, scanning or otherwise, except under the terms of the Copyright, Designs and Patents Act 1988 or under the terms of a licence issued by the Copyright Licensing Agency Ltd, 90 Tottenham Court Road, London W1T 4LP, UK, without the permission in writing of the Publisher. Requests to the Publisher should be addressed to the Permissions Department, John Wiley & Sons Ltd, The Atrium, Southern Gate, Chichester, West Sussex PO19 8SQ, England, or emailed to permreq@wiley.co.uk, or faxed to (+44) 1243 770620.

This publication is designed to provide accurate and authoritative information in regard to the subject matter covered. It is sold on the understanding that the Publisher is not engaged in rendering professional services. If professional advice or other expert assistance is required, the services of a competent professional should be sought.

#### Other Wiley Editorial Offices

John Wiley & Sons Inc., 111 River Street, Hoboken, NJ 07030, USA Jossey-Bass, 989 Market Street, San Francisco, CA 94103-1741, USA Wiley-VCH Verlag GmbH, Boschstr. 12, D-69469 Weinheim, Germany John Wiley & Sons Australia Ltd, 42 McDougall Street, Milton, Queensland 4064, Australia John Wiley & Sons (Asia) Pte Ltd, 2 Clementi Loop #02-01, Jin Xing Distripark, Singapore 129809 John Wiley & Sons Canada Ltd, 6045 Freemont Blvd, Mississauga, ONT, L5R 4J3

Wiley also publishes its books in a variety of electronic formats. Some content that appears in print may not be available in electronic books.

#### British Library Cataloguing in Publication Data

A catalogue record for this book is available from the British Library

### ISBN 978-0470-06070-4

Typeset in 10/12 pt Times by Thomson Digital, Noida, India Printed and bound in Great Britain by Antony Rowe Ltd, Chippenham, Wiltshire

# Contents

| Pr | Preface                  |                                                                                                       | xi                               |

|----|--------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------|

| Ac | cknov                    | vledgements                                                                                           | XV                               |

| 1  |                          | oduction to Finite-State Machines and State Diagrams for the Design<br>lectronic Circuits and Systems | 1                                |

|    | 1.1<br>1.2<br>1.3        | 6                                                                                                     | 1<br>2<br>21                     |

| 2  | Usir                     | ng State Diagrams to Control External Hardware Subsystems                                             | 23                               |

|    | 2.1<br>2.2<br>2.3        | 8                                                                                                     | 23<br>23<br>38                   |

| 3  | Syn                      | thesizing Hardware from a State Diagram                                                               | 39                               |

|    | 3.1<br>3.2<br>3.3        | Introduction to Finite-State Machine Synthesis<br>Learning Material<br>Summary                        | 39<br>40<br>66                   |

| 4  | Syn                      | chronous Finite-State Machine Designs                                                                 | 67                               |

|    | 4.1<br>4.2<br>4.3<br>4.4 | 4.4.1 Sampling Frequency and Samples per Waveform                                                     | 67<br>69<br>71<br>75<br>76<br>78 |

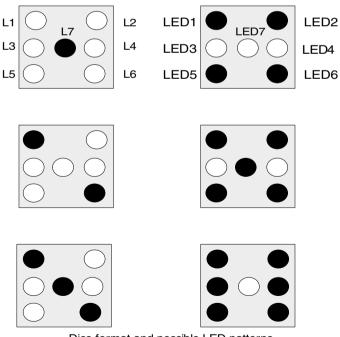

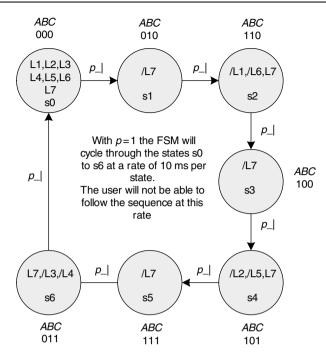

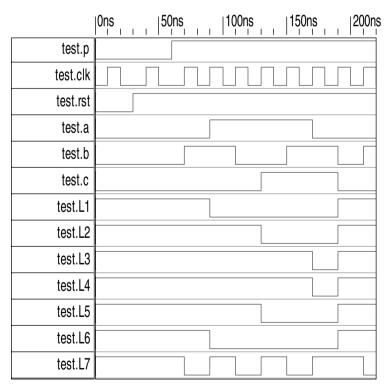

|    | 4.5                      | The Dice Game<br>4.5.1 Development of the Equations for the Dice Game                                 | 79<br>81                         |

### Contents

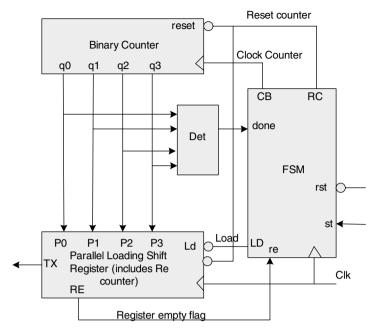

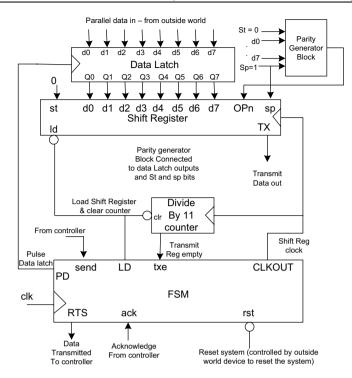

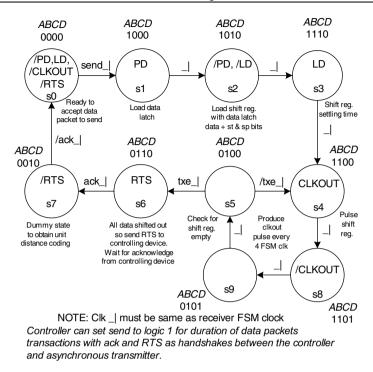

|   | 4.6                         | Binary Data Serial Transmitter                                             | 83  |

|---|-----------------------------|----------------------------------------------------------------------------|-----|

|   |                             | 4.6.1 The RE Counter Block in the Shift Register of Figure 4.15            | 87  |

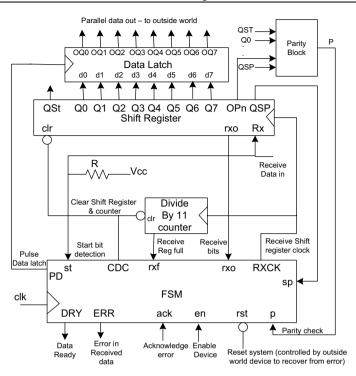

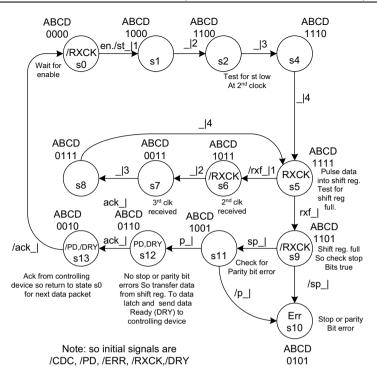

|   | 4.7                         | Development of a Serial Asynchronous Receiver                              | 88  |

|   |                             | 4.7.1 Finite-State Machine Equations                                       | 91  |

|   | 4.8                         | Adding Parity Detection to the Serial Receiver System                      | 92  |

|   |                             | 4.8.1 To Incorporate the Parity                                            | 92  |

|   |                             | 4.8.2 <i>D</i> -Type Equations for Figure 4.26                             | 94  |

|   | 4.9                         | An Asynchronous Serial Transmitter System                                  | 95  |

|   |                             | 4.9.1 Equations for the Asynchronous Serial Transmitter                    | 98  |

|   | 4.10                        | Clocked Watchdog Timer                                                     | 100 |

|   |                             | 4.10.1 <i>D</i> Flip-Flop Equations                                        | 102 |

|   |                             | 4.10.2 Output Equation                                                     | 102 |

|   | 4.11                        | Summary                                                                    | 103 |

| 5 | The                         | One Hot Technique in Finite-State Machine Design                           | 105 |

|   | 5.1                         | The One Hot Technique                                                      | 105 |

|   |                             | A Data Acquisition System                                                  | 110 |

|   |                             | A Shared Memory System                                                     | 114 |

|   |                             | Fast Waveform Synthesizer                                                  | 116 |

|   |                             | 5.4.1 Specification                                                        | 117 |

|   |                             | 5.4.2 A Possible Solution                                                  | 118 |

|   |                             | 5.4.3 Equations for the <i>d</i> Inputs to <i>D</i> Flip-Flops             | 119 |

|   |                             | 5.4.4 Output Equations                                                     | 120 |

|   | 5.5                         | Controlling the Finite-State Machine from a Microprocessor/Microcontroller | 120 |

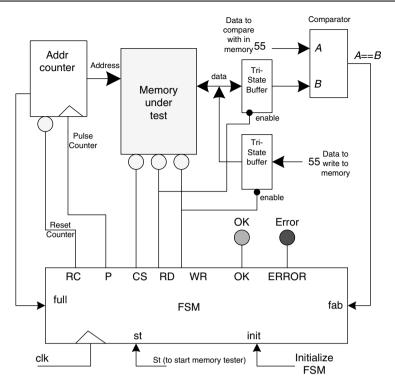

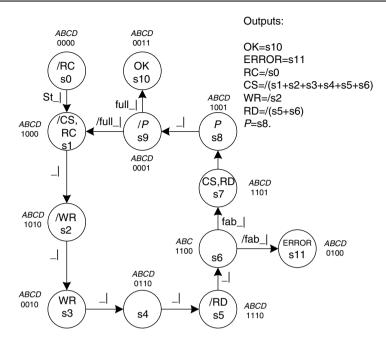

|   | 5.6                         | A Memory-Chip Tester                                                       | 123 |

|   | 5.7                         | Comparing One Hot with the more Conventional Design                        |     |

|   |                             | Method of Chapter 4                                                        | 126 |

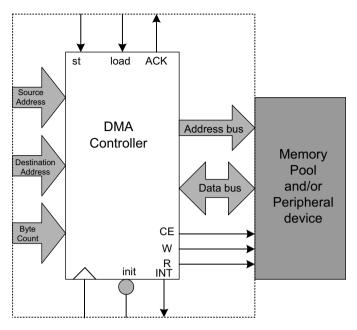

|   | 5.8                         | A Dynamic Memory Access Controller                                         | 127 |

|   |                             | 5.8.1 Flip-Flop Equations                                                  | 131 |

|   |                             | 5.8.2 Output Equations                                                     | 131 |

|   | 5.9                         | How to Control the Dynamic Memory Access from a Microprocessor             | 132 |

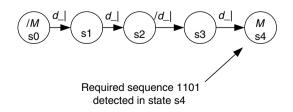

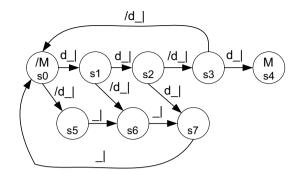

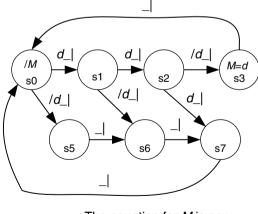

|   | 5.10                        | Detecting Sequential Binary Sequences using a Finite-State Machine         | 134 |

|   | 5.11                        | Summary                                                                    | 143 |

| 6 | Introduction to Verilog HDL |                                                                            | 145 |

|   | 6.1                         | A Brief Background to Hardware Description Languages                       | 145 |

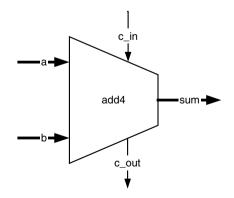

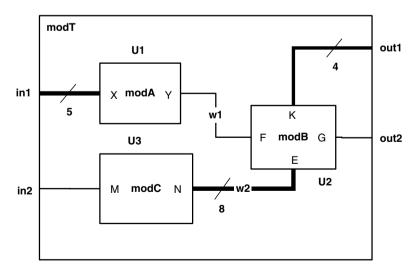

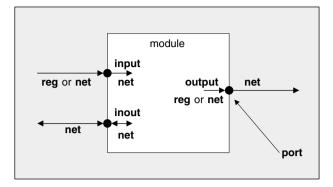

|   | 6.2                         | Hardware Modelling with Verilog HDL: the Module                            | 147 |

|   | 6.3                         | Modules within Modules: Creating Hierarchy                                 | 152 |

|   | 6.4                         | Verilog HDL Simulation: a Complete Example                                 | 155 |

|   |                             | rences                                                                     | 162 |

| 7 | Elen                        | nents of Verilog HDL                                                       | 163 |

|   | 7.1                         | Built-In Primitives and Types                                              | 163 |

|   |                             | V 1                                                                        |     |

### ii

| Contents | iii |

|----------|-----|

|          |     |

|   |            | 7.1.1 Verilog Types                                                       | 163 |

|---|------------|---------------------------------------------------------------------------|-----|

|   |            | 7.1.2 Verilog Logic and Numeric Values                                    | 167 |

|   |            | 7.1.3 Specifying Values                                                   | 169 |

|   |            | 7.1.4 Verilog HDL Primitive Gates                                         | 170 |

|   | 7.2        | Operators and Expressions                                                 | 172 |

|   |            | Example Illustrating the Use of Verilog HDL Operators:                    | 1,- |

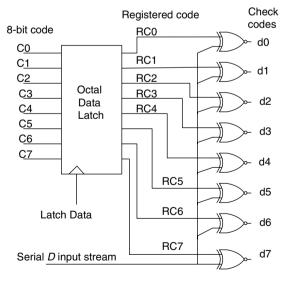

|   | 1.0        | Hamming Code Encoder                                                      | 185 |

|   |            | 7.3.1 Simulating the Hamming Encoder                                      | 188 |

|   | Refe       | rences                                                                    | 195 |

|   | Refe       |                                                                           | 175 |

| 8 | Desc       | ribing Combinational and Sequential Logic using Verilog HDL               | 197 |

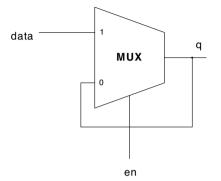

|   | 8.1        | The Data-Flow Style of Description: Review of the Continuous Assignment   | 197 |

|   | 8.2        | The Behavioural Style of Description: the Sequential Block                | 198 |

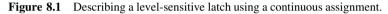

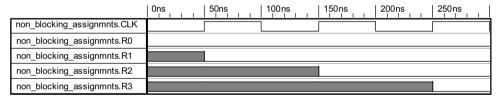

|   | 8.3        | Assignments within Sequential Blocks: Blocking and Nonblocking            | 204 |

|   |            | 8.3.1 Sequential Statements                                               | 204 |

|   | 8.4        | Describing Combinational Logic using a Sequential Block                   | 209 |

|   | 8.5        | Describing Sequential Logic using a Sequential Block                      | 217 |

|   |            | Describing Memories                                                       | 229 |

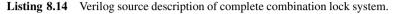

|   | 8.7        | Describing Finite-State Machines                                          | 240 |

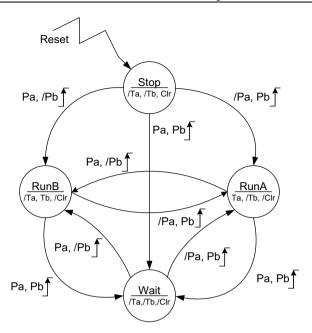

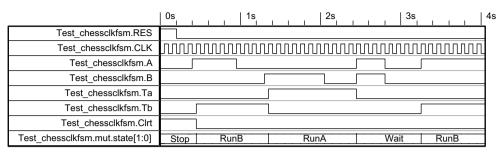

|   |            | 8.7.1 Example 1: Chess Clock Controller Finite-State Machine              | 245 |

|   |            | 8.7.2 Example 2: Combination Lock Finite-State Machine with               |     |

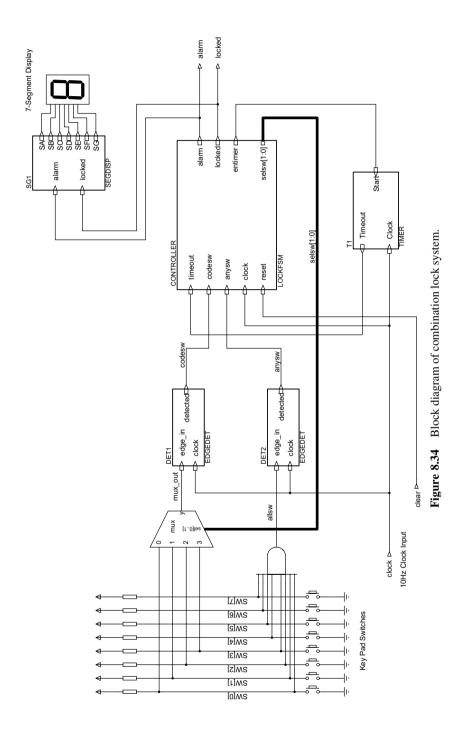

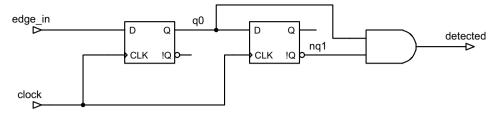

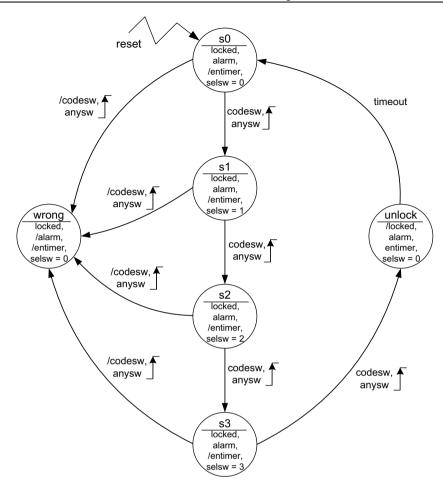

|   |            | Automatic Lock Feature                                                    | 252 |

|   | Refe       | rences                                                                    | 265 |

| 9 | Asvr       | chronous Finite-State Machines                                            | 267 |

| 1 | •          | Introduction                                                              |     |

|   | 9.1        |                                                                           | 267 |

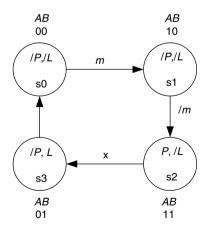

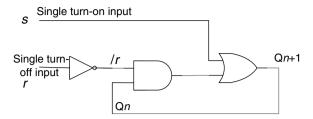

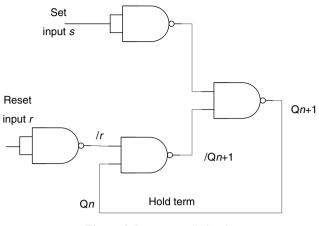

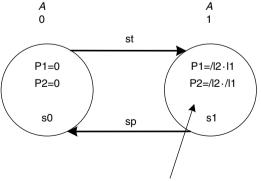

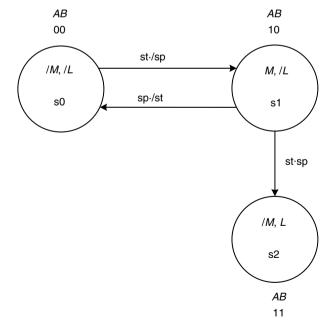

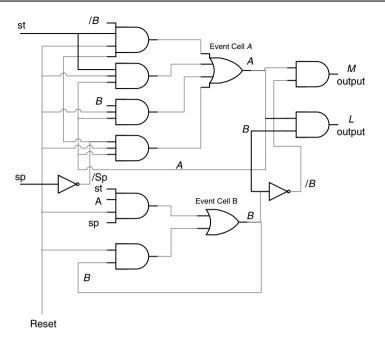

|   | 9.2        | Development of Event-Driven Logic                                         | 269 |

|   | 9.3        | Using the Sequential Equation to Synthesize an Event Finite-State Machine | 272 |

|   | 0.4        | 9.3.1 Short-cut Rule                                                      | 275 |

|   | 9.4        | Implementing the Design using Sum of Product as used                      | 070 |

|   |            | in a Programmable Logic Device                                            | 276 |

|   | o <b>r</b> | 9.4.1 Dropping the Present State $n$ and Next State $n + 1$ Notation      | 277 |

|   | 9.5        | Development of an Event Version of the Single-Pulse Generator with        |     |

|   |            | Memory Finite-State Machine                                               | 277 |

|   | 9.6        | Another Event Finite-State Machine Design from Specification              |     |

|   |            | through to Simulation                                                     | 280 |

|   |            | 9.6.1 Important Note!                                                     | 280 |

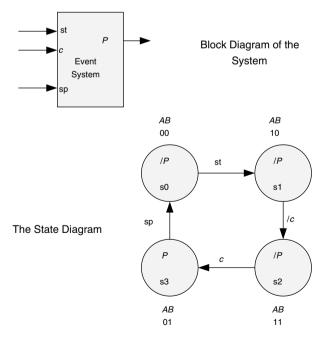

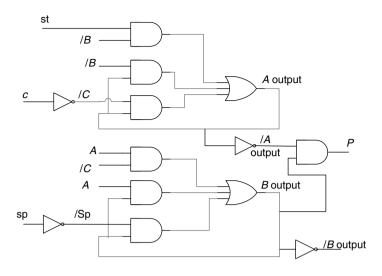

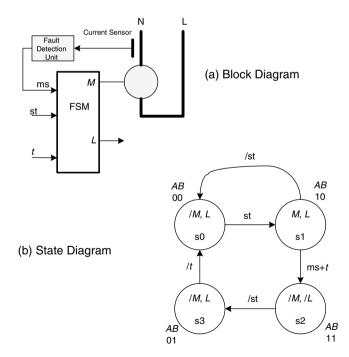

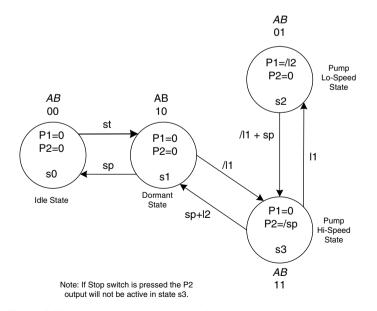

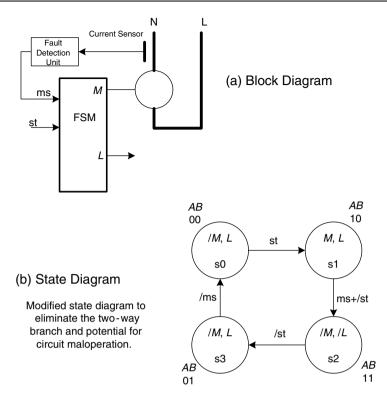

|   |            | 9.6.2 A Motor Controller with Fault Current Monitoring                    | 281 |

|   | 9.7        | The Hover Mower Finite-State Machine                                      | 285 |

|   |            | 9.7.1 The Specification and a Possible Solution                           | 285 |

|   | 9.8        | An Example with a Transition without any Input                            | 289 |

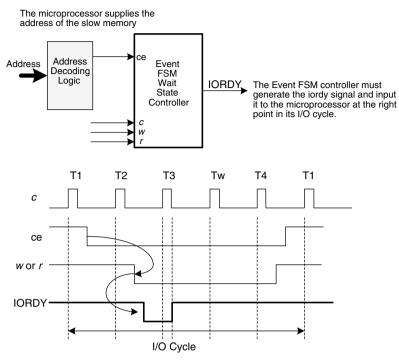

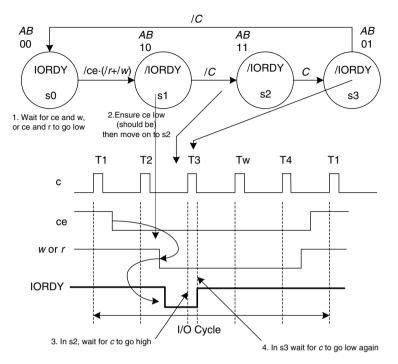

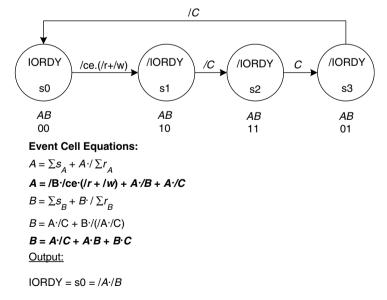

|   | 9.9        | Unusual Example: Responding to a Microprocessor-Addressed Location        | 291 |

|   | 9.10       | An Example that uses a Mealy Output                                       | 293 |

|   |            | 9.10.1 Tank Water Level Control System with Solutions                     | 293 |

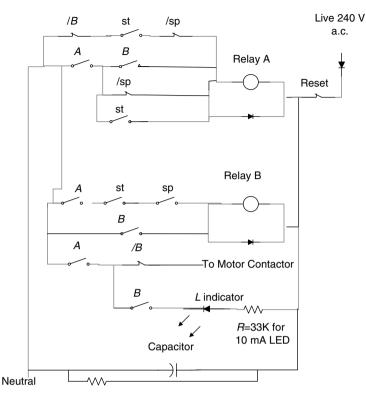

|   | 9.11       | An Example using a Relay Circuit                                          | 296 |

|   |            |                                                                           |     |

| iv Contents |  |

|-------------|--|

|-------------|--|

|    | 9.12  | Race Conditions in an Event Finite-State Machine                    | 299 |

|----|-------|---------------------------------------------------------------------|-----|

|    |       | 9.12.1 Race between Primary Inputs                                  | 300 |

|    |       | 9.12.2 Race between Secondary State Variables                       | 300 |

|    |       | 9.12.3 Race between Primary and Secondary Variables                 | 300 |

|    | 9.13  | Wait-State Generator for a Microprocessor System                    | 301 |

|    | 9.14  | Development of an Asynchronous Finite-State Machine                 |     |

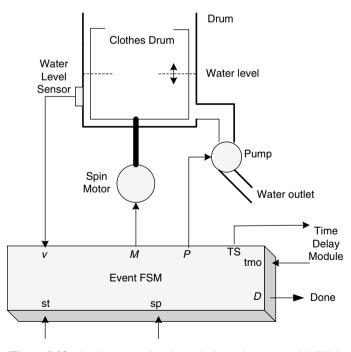

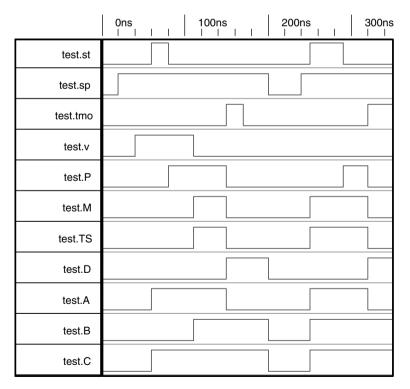

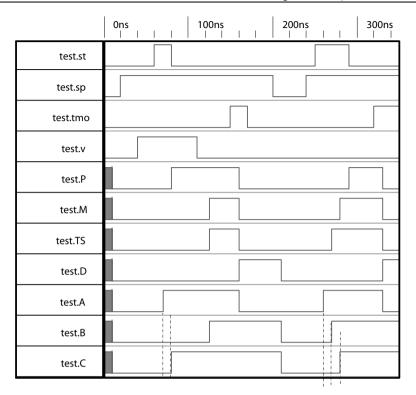

|    |       | for a Clothes Spinner System                                        | 304 |

|    | 9.15  | Caution when using Two-Way Branches                                 | 309 |

|    |       | Summary                                                             | 312 |

|    | Refe  | prences                                                             | 312 |

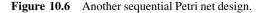

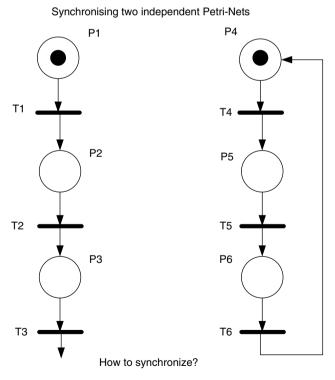

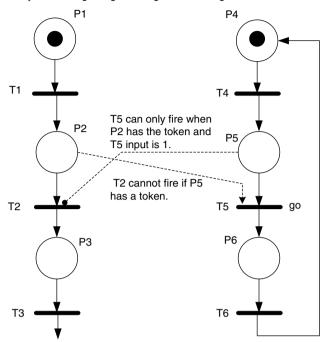

| 10 | Intro | oduction to Petri Nets                                              | 313 |

|    | 10.1  | Introduction to Simple Petri Nets                                   | 313 |

|    |       | Simple Sequential Example using a Petri Net                         | 318 |

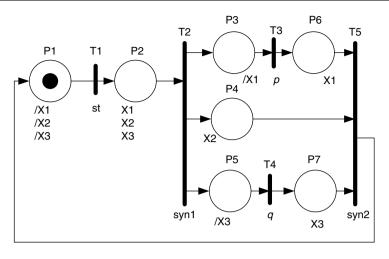

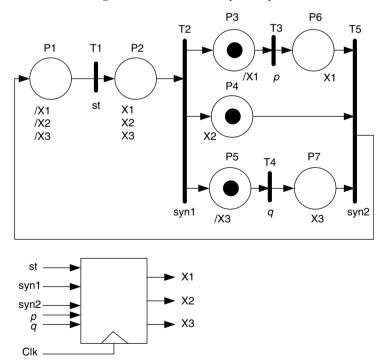

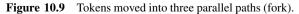

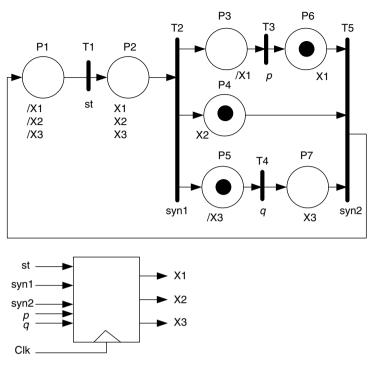

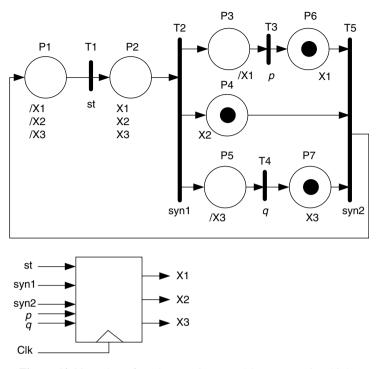

|    |       | Parallel Petri Nets                                                 | 319 |

|    |       | 10.3.1 Another Example of a Parallel Petri Net                      | 323 |

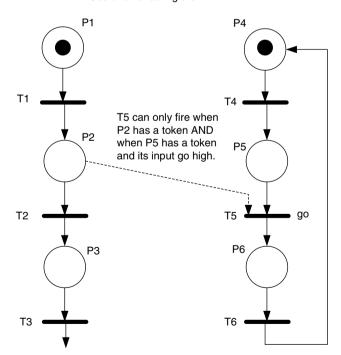

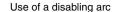

|    | 10.4  | Synchronizing Flow in a Parallel Petri Net                          | 324 |

|    |       | 10.4.1 Enabling and Disabling Arcs                                  | 325 |

|    | 10.5  | Synchronization of Two Petri Nets using Enabling and Disabling Arcs | 326 |

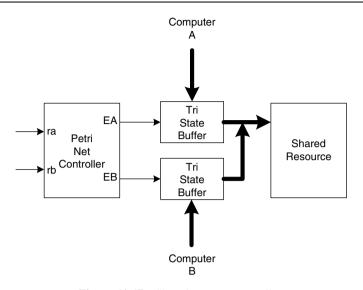

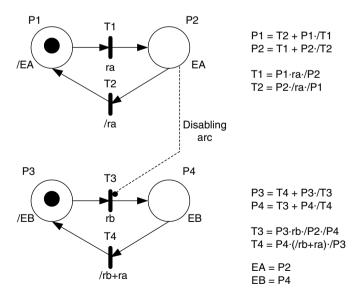

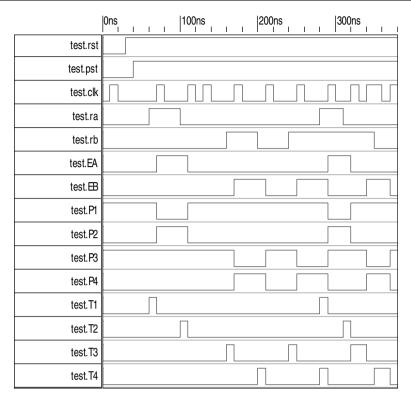

|    | 10.6  | Control of a Shared Resource                                        | 327 |

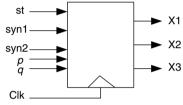

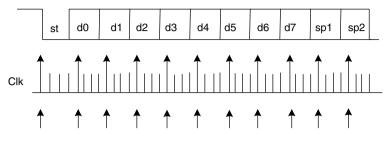

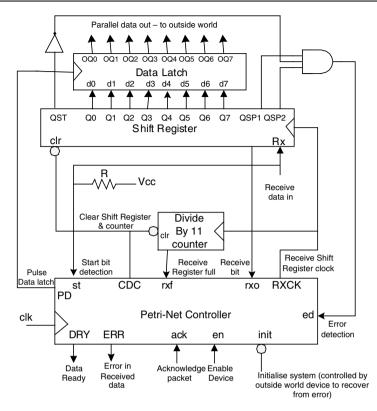

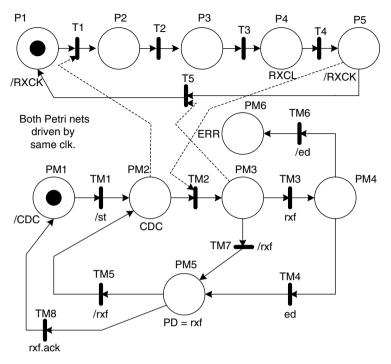

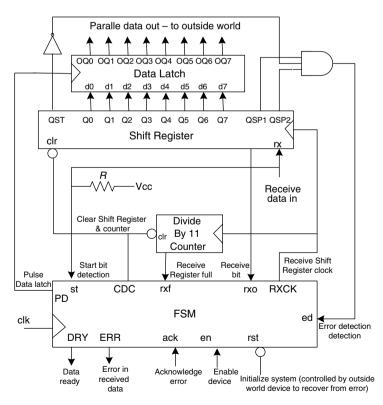

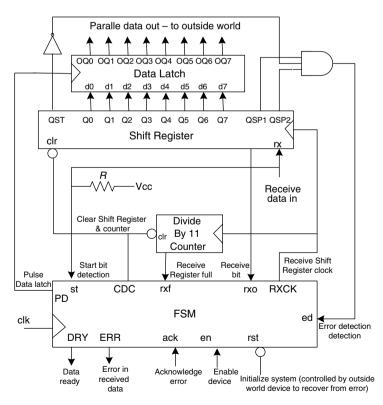

|    | 10.7  | A Serial Receiver of Binary Data                                    | 329 |

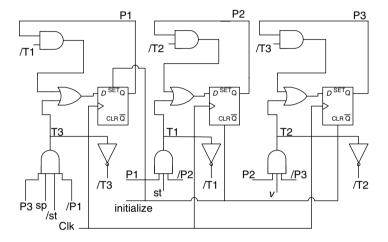

|    |       | 10.7.1 Equations for the First Petri Net                            | 333 |

|    |       | 10.7.2 Output                                                       | 333 |

|    |       | 10.7.3 Equations for the Main Petri Net                             | 333 |

|    |       | 10.7.4 Outputs                                                      | 333 |

|    |       | 10.7.5 The Shift Register                                           | 334 |

|    |       | 10.7.6 Equations for the Shift Register                             | 334 |

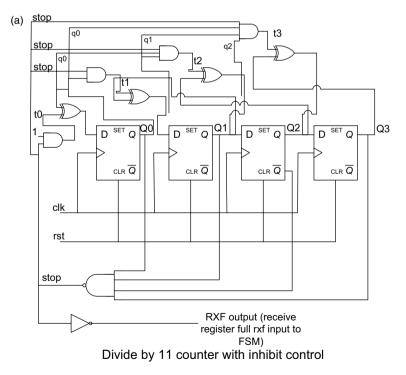

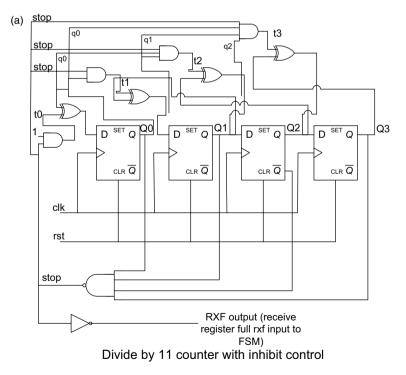

|    |       | 10.7.7 The Divide-by-11 Counter                                     | 335 |

|    |       | 10.7.8 The Data Latch                                               | 335 |

|    | 10.8  | Summary                                                             | 336 |

|    | Refe  | erences                                                             | 336 |

| Ар | pend  | ix A: Logic Gates and Boolean Algebra Used in the Book              | 337 |

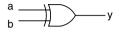

|    | A.1   | Basic Gate Symbols Used in the Book with Boolean Equations          | 337 |

|    | A.2   | The Exclusive OR and Exclusive NOR                                  | 338 |

|    |       | Laws of Boolean Algebra                                             | 338 |

|    |       | A.3.1 Basic OR Rules                                                | 339 |

|    |       | A.3.2 Basic AND Rules                                               | 339 |

|    |       | A.3.3 Associative and Commutative Laws                              | 340 |

|    |       | A.3.4 Distributive Laws                                             | 340 |

|    |       | A.3.5 Auxiliary Law for Static 1 Hazard Removal                     | 341 |

|    |       | A.3.5.1 Proof of Auxiliary Rule                                     | 341 |

|    |       | A.3.6 Consensus Theorem                                             | 342 |

|    |       | A.3.7 The Effect of Signal Delay in Logic Gates                     | 343 |

|    |       | A.3.8 De Morgan's Theorem                                           | 343 |

| A.4         | Examples of Applying the Laws of Boolean Algebra                      | 345        |

|-------------|-----------------------------------------------------------------------|------------|

|             | A.4.1 Example: Converting AND–OR to NAND                              | 345        |

|             | A.4.2 Example: Converting AND–OR to NOR                               | 345        |

|             | A.4.3 Logical Adjacency Rule                                          | 345        |

| A.5         | Summary                                                               | 346        |

| Append      | ix B: Counting and Shifting Circuit Techniques                        | 347        |

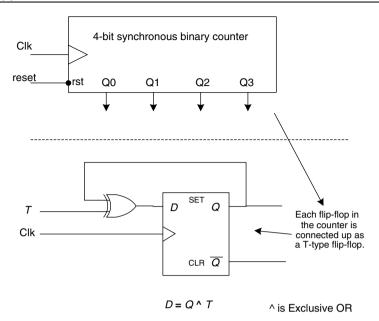

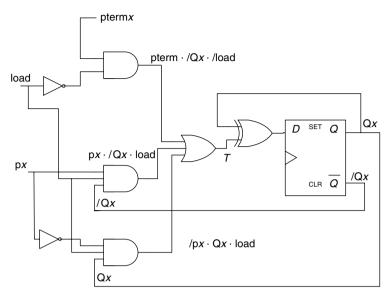

| B.1         | Basic Up and Down Synchronous Binary Counter Development              | 347        |

| B.2         | Example for a 4-Bit Synchronous Up-Counter Using T-Type Flip-Flops    | 349        |

| B.3         | Parallel-Loading Counters: Using T Flip-Flops                         | 352        |

| B.4         | Using D Flip-Flops to Build Parallel-Loading Counters with Cheap      |            |

|             | Programmable Logic Devices                                            | 353        |

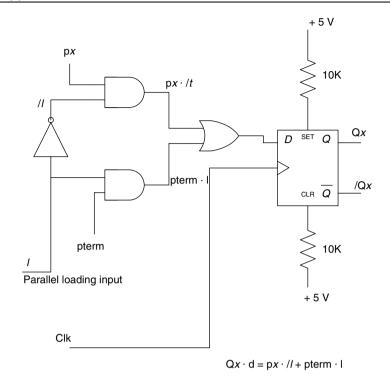

| B.5         | Simple Binary Up-Counter: with Parallel Inputs                        | 354        |

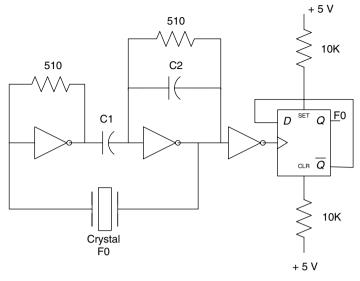

| B.6         | Clock Circuit to Drive the Counter (And Finite-State Machines)        | 355        |

| B.7         | e e                                                                   | 355        |

| B.8         | e                                                                     | 357        |

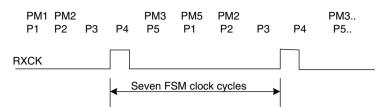

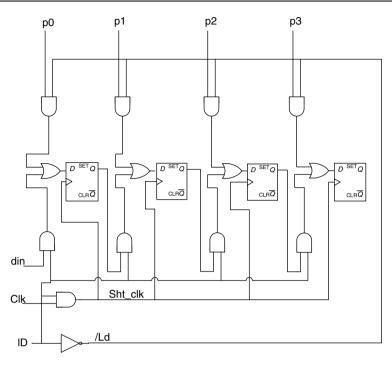

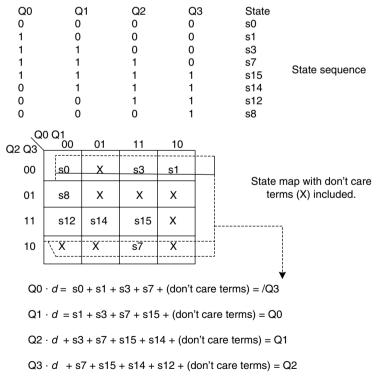

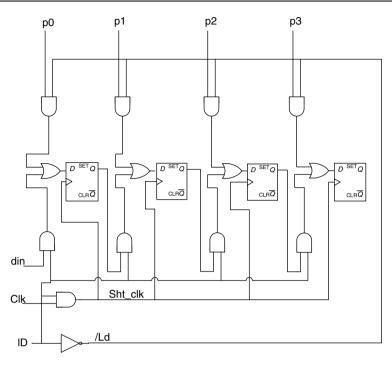

| B.9         | Asynchronous Receiver Details of Chapter 4                            | 358        |

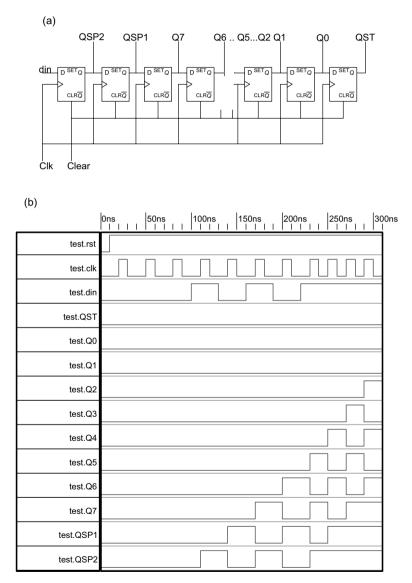

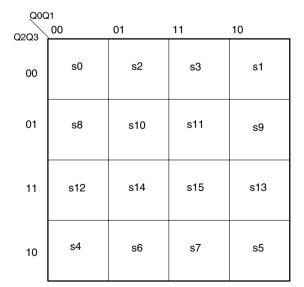

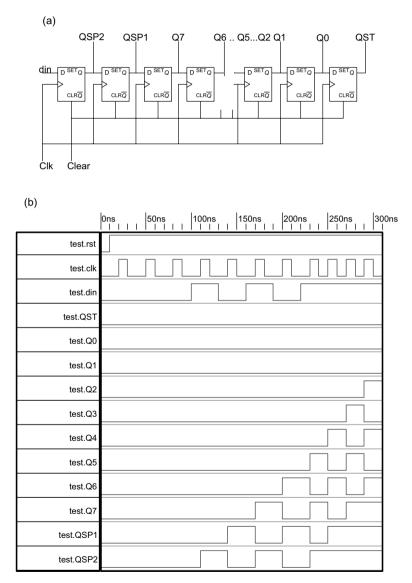

|             | B.9.1 The 11-Bit Shift Registers for the Asynchronous Receiver Module | 360        |

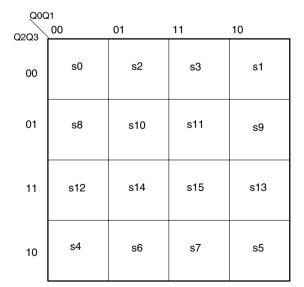

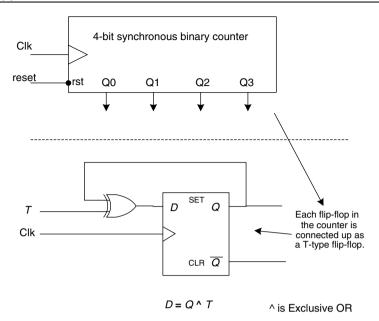

|             | B.9.2 Divide-by-11 Counter                                            | 362        |

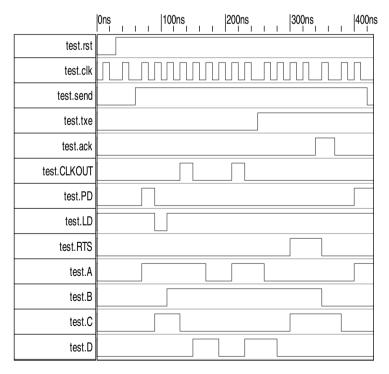

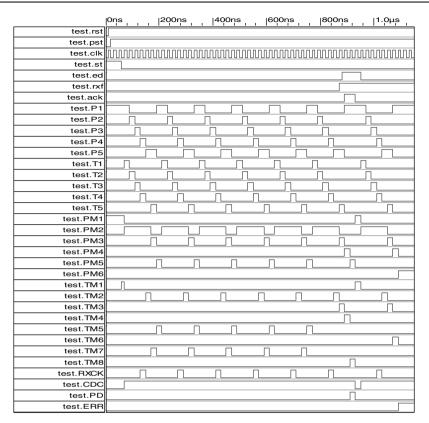

|             | B.9.3 Complete Simulation of the Asynchronous Receiver Module         |            |

|             | of Chapter 4                                                          | 364        |

| B.10        | Summary                                                               | 365        |

| Append      | ix C: Tutorial on the Use of Verilog HDL to Simulate a                |            |

| Finite-S    | tate Machine Design                                                   | 367        |

| <b>C</b> .1 | Introduction                                                          | 367        |

| C.2         |                                                                       | 201        |

|             | Design: Using Verilog HDL to Simulate                                 | 367        |

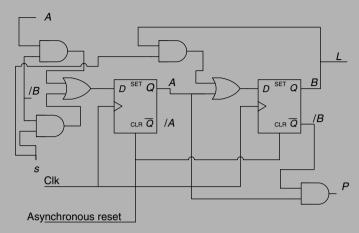

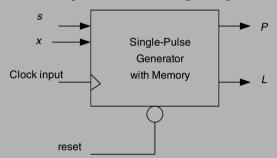

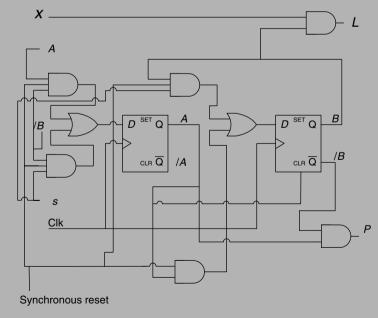

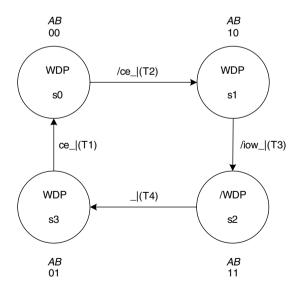

|             | C.2.1 Specification                                                   | 367        |

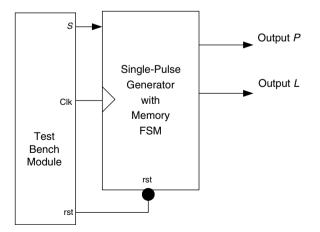

|             | C.2.2 Block Diagram                                                   | 367        |

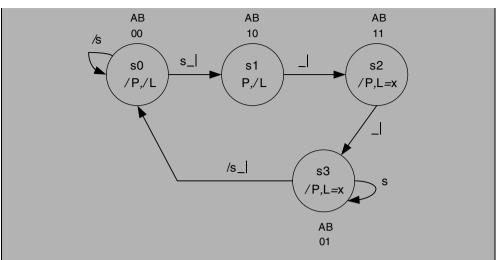

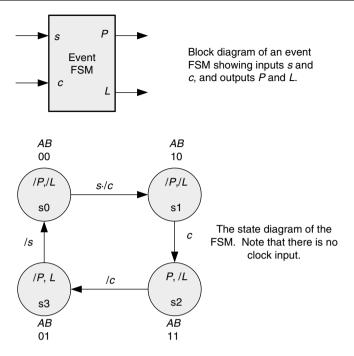

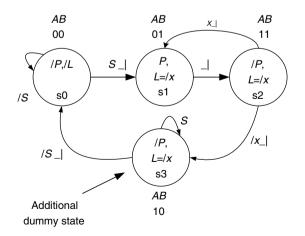

|             | C.2.3 State Diagram                                                   | 368        |

|             | C.2.4 Equations from the State Diagram                                | 368        |

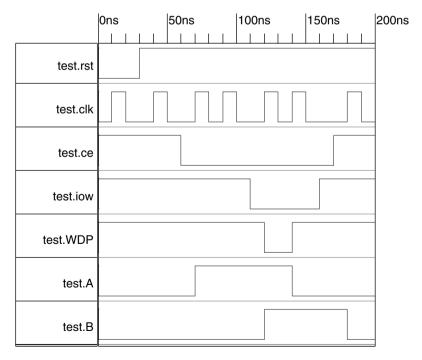

|             | C.2.5 Translation into a Verilog Description                          | 369        |

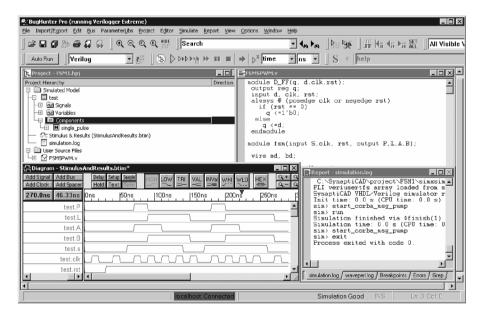

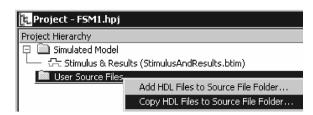

| C.3         |                                                                       | 372        |

| C.4         | 1                                                                     | 376        |

| C.5         |                                                                       | 378        |

| Append      | ix D: Implementing State Machines using Verilog Behavioural Mode      | 379        |

| D.1         | Introduction                                                          | 379        |

| D.2         | The Single-Pulse/Multiple-Pulse Generator with Memory Finite-State    | 2.7        |

| 2.2         | Machine Revisited                                                     | 379        |

| D.3         |                                                                       |            |

|             | The Memory Tester Finite-State Machine in Section 5.6                 | 383        |

| D.4         | The Memory Tester Finite-State Machine in Section 5.6<br>Summary      | 383<br>386 |

### Preface

This book covers the design and use of finite state-machines (FSMs) in digital systems. It includes stand-alone applications and systems that use microprocessors, microcontrollers, and memory controlled directly from the FSM, as well as other common situations found in practical digital systems. The emphasis is on obtaining a good understanding of FSMs, how they can be used, and where to use them.

The popular and widely used Verilog hardware description language (HDL) is introduced and applied to the description and verification of many of the designs in the book. In addition to logic gate and Boolean equation-level styles of Verilog description, there is also a chapter covering the use of HDL at the so-called behavioural level, whereby a design is described using the high-level features provided by Verilog HDL.

There is also a chapter using the One Hot technique, commonly used to implement FSMs in field programmable gate arrays with examples on the development of dynamic memory access (DMA) controllers and data sequence detectors. Asynchronous (event-driven) FSMs not requiring a clock signal are covered in a chapter using a technique that allows rapid development of reliable systems. A chapter on the use of Petri-net-based controllers is included, allowing parallel-based digital FSMs to be developed.

In the development of digital systems, microcontrollers have been used for many years to control digital inputs and outputs, as well as process analogue information. Now, using the techniques in this book, FSM-based designs can be implemented using a deterministic model, the state diagram, as a design aid. Once developed, the state diagram can be used to implement the final system using either Boolean equations obtained directly from the state diagram. External devices, such as memory, address counters and comparators, can be implemented either from the Boolean equations that define their operation or via behavioural-level descriptions in Verilog HDL.

The book is targeted at undergraduate final-year students of Electrical, Electronic, and Communications Electronic Engineering, as well as postgraduate students and practising Electronic Design Engineers who want to know how to develop FSM-based systems quickly. The book will assume an understanding of basic logic design and Boolean algebra, as would be expected of a final-year undergraduate. The book sequence follows.

The first three chapters are in the form of a linear frame programmed learning format to help the reader learn the essential concepts of synchronous FSM design.

This set of notes has been used with undergraduate final-year students at our university for some years now and has been well received by the students. These chapters cover the idea of basic FSM design and synthesis. Once this is covered, the book reverts to a more familiar text. However, the first three chapters, being linear, can be read in the same style as the more familiar text if the reader desires.

A breakdown of the chapters in the book now follows.

Chapter 1 contains an introduction to FSMs, the Mealy and Moore models of an FSM, differences between synchronous (clock-driven) FSMs and asynchronous (event-driven) FSMs, the state diagram and how it can be used to indicate sequential behaviour and the inputs and outputs of a system. This follows with a number of examples of FSMs to illustrate the way in which they can be developed to meet particular specifications.

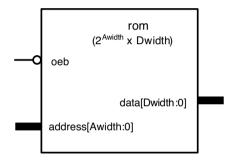

Chapter 2 covers the use of external hardware and how this hardware can be controlled by the FSM. The examples include how to create wait states using external timers, how to control analogue-to-digital converters, and memory devices. This opens up the possibilities of FSM-based systems that are not normally covered in other books.

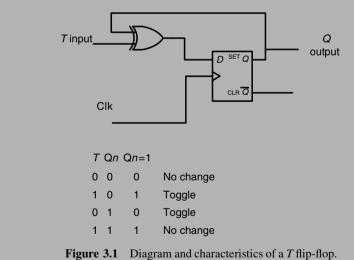

Chapter 3 is a continuation of the programmed learning text, looking at synthesization of state diagrams using T flip-flops and D flip-flops, as well as initialization techniques.

The remaining chapters of the book will be in a more conventional format.

Chapter 4 covers synchronous (clock-driven) FSM examples, some with simulation. This chapter gives some practical examples commonly found in real applications, such as a digital waveform synthesizer and asynchronous serial transmit and receive blocks.

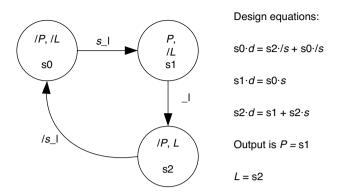

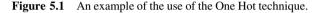

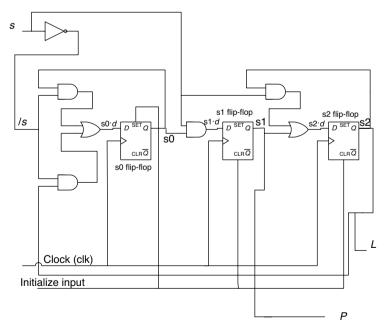

Chapter 5 is an introduction to the use of 'One Hotting' in synchronous FSM design. Amongst the examples covered is a DMA controller and serial bit stream code detection.

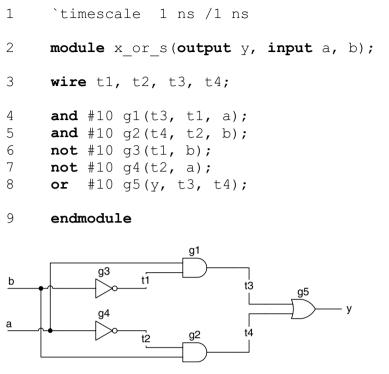

Chapter 6 is an introduction to Verilog HDL and how to use it at the gate level and the Boolean equation level, together with how to combine different modules to form a complete system.

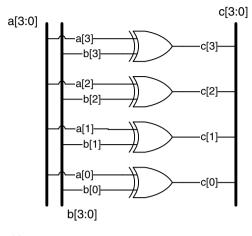

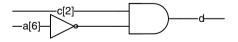

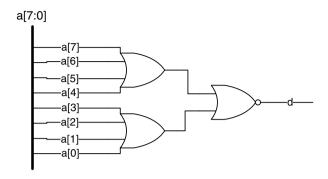

Chapter 7 introduces the basic lexical elements of the Verilog HDL. Emphasis is placed on those aspects of the language that support the description of synthesizable combinational and sequential logic.

Chapter 8 takes a more detailed look at the Verilog HDL, with emphasis on behavioural modelling of FSM designs. It covers using an HDL to implement synchronous FSMs at the behavioural level - with examples.

Chapter 9 is an introduction to asynchronous (event-driven) design of FSMs from initial concepts through to the design of asynchronous FSMs to given specifications. This will also include a brief discussion of race problems with asynchronous designs and how to overcome them.

Chapter 10 is an introduction to synchronous Petri nets, and how they can be used to implement both sequential and parallel FSMs. Petri nets allow the design of parallel FSMs with synchronized control. This chapter shows how a Petri net can be designed and synthesized as an electronic circuit using *D*-type flip-flops.

Each chapter contains examples with solutions, many of which have been used by the authors in real practical systems.

There is a CD-ROM included with the book containing a digital simulation program to aid the reader in learning and verifying the many examples given in the book. The program is based on Verilog HDL. This tool has been used to simulate most of the examples in the book.

Also on the CD-ROM are folders containing many of the book's examples, complete with test-bench descriptions to allow the simulations to be run directly on a PC-based computer.

Peter Minns BSc(H) PhD CEng MIET Ian Elliott BSc(H) MPhil CEng MIET Newcastle Upon Tyne

## Acknowledgements

We would like to thank all those who have helped in the proof reading of this book. In particular, we thank Safwat Mansi for his proof reading of our ideas and his helpful suggestions. In addition, Kathleen Minns is thanked for her help in the proof reading of the entire manuscript.

We would like to thank our editors, Emily Bone, Laura Bell, Kate Griffiths and Nicky Skinner for their help over the time that we have worked on this book. Thanks also to Caitlin Flint for her help with the marketing of the book.

Special thanks go to Donna Mitchell at SynaptiCAD for her help with Appendix C on the use of the VeriLoger Extreme Simulation Program on the CD-ROM with this book. Also, Gary Covington for his help in creating the CD-ROM.

Finally, thanks to our wives, Helen and Kathleen, for putting up with our frequent disappearances during the preparation of the book.

Any errors are, of course, entirely the responsibility of the authors.

# **1** Introduction to Finite-State Machines and State Diagrams for the Design of Electronic Circuits and Systems

### 1.1 INTRODUCTION

This chapter, and Chapters 2 and 3, is written in the form of a linear frame, programmed learning text. The reason for this is to help the reader to learn the basic skills required to design clocked finite-state machines (FSMs) so that they can develop their own designs based on traditional T flip-flops and D flip-flops. Later, other techniques will be introduced, such as One Hot, asynchronous FSMs, and Petri nets; these will be developed along the same lines as the work covered in this chapter, but not using the linear frame, programmed learning format.

The text is organized into frames, each frame following on consecutively from the previous one, but at times the reader may be redirected to other frames, depending upon the response to the questions asked. It is possible, however, to read the programmed learning chapters as a normal book.

There are *tasks* set throughout the frames to test your understanding of the material.

To make it easier to identify input and output signals, inputs will be in lowercase and outputs in uppercase.

Please read the Chapters 1–3 first and attempt all the questions before moving on to the later chapters. The reason for this approach is that the methods used in the book are novel, powerful, and when used correctly can lead to a rapid approach to the design of digital systems that use FSMs.

Chapters 1–5, 9 and 10 make use of techniques to develop FSM-based systems at the equation and gate level, where the designer has complete control of the design.

Chapters 6–8 can be read as a self-contained study of the Verilog hardware description language (HDL).

FSM-based Digital Design using Verilog HDL Peter Minns and Ian Elliott

<sup>© 2008</sup> John Wiley & Sons, Ltd. ISBN: 978-0-470-06070-4

### 1.2 LEARNING MATERIAL

### Frame 1.1 What is an FSM?

An FSM is a digital sequential circuit that can follow a number of predefined states under the control of one or more inputs. Each state is a stable entity that the machine can occupy. It can move from this state to another state under the control of an outside-world input.

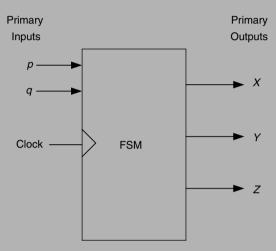

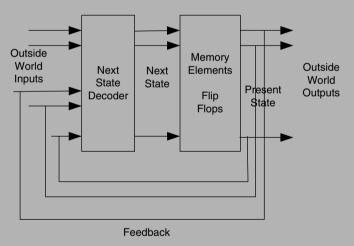

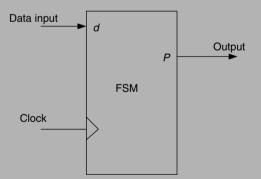

Figure 1.1 Block diagram of an FSM-based application.

Figure 1.1 shows an FSM with three outside-world inputs p, q, and the clock, and three outside-world outputs X, Y, and Z are shown. Note that some FSMs have a clock input and are called synchronous FSMs, i.e. those that do not belong to a type of FSM called asynchronous FSMs. However, most of this text will deal with the more usual synchronous FSMs, which *do* have a clock input. Asynchronous FSMs will be dealt with later in the book.

As noted above, inputs use lower case and output upper case names.

A synchronous FSM can move between states only if a clock pulse occurs.

*Task* Draw a block diagram for an FSM with five inputs x, y, z, t, and a clock, and with two outputs P and Q.

Go to Frame 1.2 after attempting this question.

### Frame 1.2

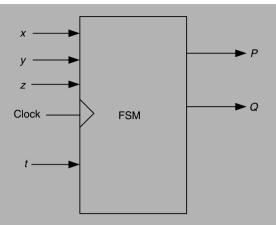

The FSM with five inputs x, y, z, t, and a clock, and with two outputs P and Q is shown in Figure 1.2.

Figure 1.2 Block diagram with inputs, outputs, and a clock input.

The reader may wish to go back and reread Frame 1.1 if the answer was incorrect.

Each state of the FSM needs to be identifiable. This is achieved by using a number of internal (to the FSM block) flip-flops. An FSM with four states would require two flip-flops, since two flip-flops can store  $2^2 = 4$  state numbers. Each state has a unique state number, and states are usually assigned numbers as s0 (state 0), s1, s2, and s3 (for the four-state example).

The rule here is

Number of states  $= 2^{\text{Number of flip-flops}}$ ,

for which

Number of flip flops =

$$\frac{\log_{10}(\text{Number of states})}{\log_{10}(2)}$$

So an FSM with 13 states would require  $2^4$  flip-flops (i.e. 16 states, of which 13 are used in the FSM); that is:

Number of flip flops

$$=\frac{\log_{10}(13)}{\log_{10}(2)} = 3.7.$$

This must be rounded up to the nearest integer, i.e. 4.

*Tasks* 1. How many flip-flops would be required for an FSM using 34 states?2. What would the state numbers be for this FSM?

2. What would the state numbers be for this 151

After answering these questions, go to Frame 1.3.

### Frame 1.3

The answers to the questions are as follows:

1. How many flip-flops would be required for an FSM using 34 states?

$2^6 = 64$

would accommodate 34 states. In general:

$2^4 = 16$  states,  $2^5 = 32$  states,  $2^6 = 64$  states,  $2^7 = 128$  states, etc.

2. What would the state numbers be for this FSM?

These would be

s0, s1, s2, s3, s4, s5, s6, s7, s8, s9, s10, s11, s12, s13, s14, s15, s16, s17, s18, s19, s20, s21, s22, s23, s24, s25, s26, s27, s28, s29, s30, s31, s32, s33.

The unused states would be s34–s63.

Note, in this book, lower case 's' will be used to represent states to avoid confusion of state s0 with the word 'so' or 'So'.

As well as containing flip-flops to define the individual states of the FSM uniquely, there is also combinational logic that defines the outside-world outputs. In addition, the outside-world inputs connect to combinational logic to supply the flip-flops inputs.

Go to Frame 1.4.

### Frame 1.4

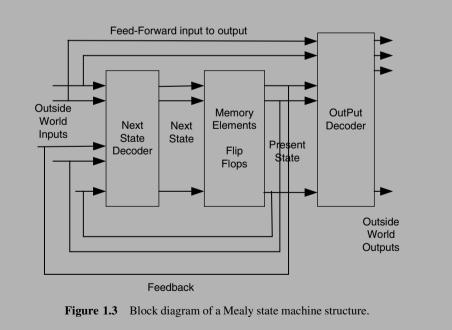

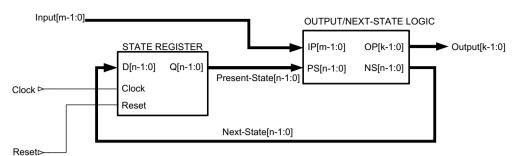

Figure 1.3 illustrates the internal architecture for a Mealy FSM.

This diagram shows that the FSM has a number of inputs that connect to the Next State Decoder (combinational) logic. The Q outputs of the memory element Flip-Flops connect to the Output Decoder logic, which in turn connects to the Outside World Outputs.

The Flip-Flops outputs are used as Next State inputs to the Next State Decoder, and it is these that determine the next state that the FSM will move to. Once the FSM has moved to this Next State, its Flip-Flops acquire a new Present State, as dictated by the Next State Decoder.

Note that some of the Outside World Inputs connect directly to the Output Decoder logic. This is the main feature of the Mealy-type FSM.

Go to Frame 1.5.

### Frame 1.5

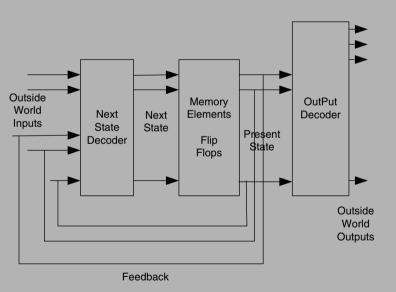

Another architectural form for an FSM is the Moore FSM.

The Moore FSM (Figure 1.4) differs from the Mealy FSM in that it does not have the feed-forward paths.

Figure 1.4 Block diagram of a Moore state machine structure.

This type of FSM is very common. Note that the Outside World Outputs are a function of the Flip-Flops outputs only (unlike the Mealy FSM architecture, where the Outside World Outputs are a function of Flip-Flops outputs *and* some Outside World Inputs). Both the Moore and Mealy FSM designs will be investigated in this book. Go to Frame 1.6.

### Frame 1.6

Complete the following:

A Moore FSM differs to that of a Mealy FSM in that it has

This means that the Moore FSM outputs depend on

whereas the Mealy FSM outputs can depend upon \_\_\_\_\_\_ Go back and read Frame 1.4 and Frame 1.5 for the solutions.

### Frame 1.7

Look at the Moore FSM architecture again, but with removal of all of the Outside World Inputs, apart from the clock. Also remove the Output Decoding logic. What is left should be a very familiar architecture. This is shown in Figure 1.5.

Figure 1.5 Block diagram of a Class C state-machine structure.

This architecture is in fact the synchronous counter that is used in many counter applications. Note that an Up/Down counter would have the additional outside-world input 'Up/ Down', which would be used to control the direction of counting.

The Flip-Flops outputs in this architecture are used to connect directly to the outsideworld. Note that, in a synchronous (clock-driven) FSM, one of the inputs would be the clock. Go to Frame 1.8.

7

### Frame 1.8

Historically, two types of state diagram have evolved: one for the design of Mealy FSMs and one for the design of Moore-type FSMs. The two are known as *Mealy state* diagrams and *Moore state* diagrams respectively.

These days, a more general type of state diagram can be used to design both the Mealy and Moore types of FSM. This is the type of state diagram that will be used throughout the remainder of this book.

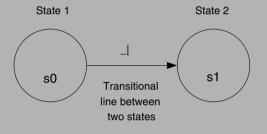

A state diagram shows each state of the FSM and the transitions to and from that state to other states. The states are usually drawn as circles (but some people like to use a square box) and the transition between states is shown as an arrowed line connecting the states (Figure 1.6).

Figure 1.6 Transition between states.

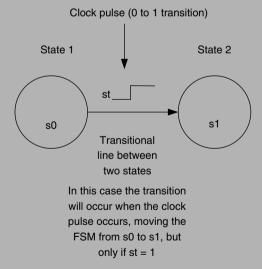

In addition to the transitional line between states there is an input signal name (Figure 1.7).

In the above diagram, the transition between state s0 and s1 will occur only if the Outside World Input st = 1 and a 0-to -1 transition occurs on the clock input.

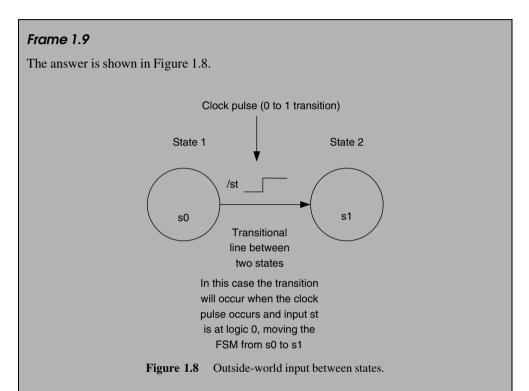

*Task* What changes would be needed to the state diagram of Figure 1.9 to make the transition between s0 and s1 occur when input st = 0?

After attempting this question, go to Frame 1.9.

Here, st has been replaced with /st, indicating that st must be logic 0 before a transition to s1 can take place), i.e. /st means 'NOT st'; hence, when st = 0, /st = 1.

Note that outside-world inputs always lie along the transitional lines.

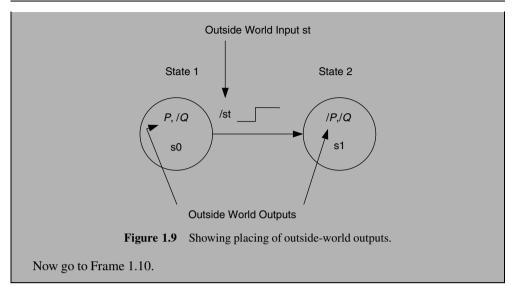

The state diagram must also show how the outside-world outputs are affected by the state diagram. This is achieved by placing the outside-world outputs either

- inside the state circle/square (Figure 1.9), or

- alongside the state circle/square.

In this diagram, outside-world outputs P and Q are shown inside the state circles. In this particular case, P is logic 1 in state s0, and changes to logic 0 when the FSM moves to state s1. Output Q does not change in the above transaction, remaining at logic 0 in both states.

Inputs like st are primary inputs; outputs like P and Q are primary outputs.

*Task* Draw a block diagram showing inputs and outputs for the state diagram of Figure 1.9.

### Frame 1.10

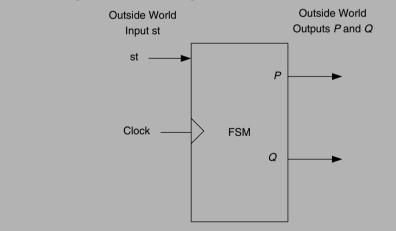

The block diagram will look like Figure 1.10.

Figure 1.10 The block diagram for state diagram of Figure 1.9.

This is easily obtained from the state diagram since inputs are located along transitional lines and outputs inside (or along side) the state circle.

Recall that in Frame 1.2 each state had to have a unique state number and that a number of flip-flops were needed to perform this task. These flip-flops are part of the internal design of the FSM and are used to produce an internal count sequence (they are essentially acting like a synchronous counter, but one that is controlled by the outside-world inputs). The internal count sequence produced by the flip-flops is used to control the outside-world decoder so that outputs can be turned on and off as the FSM moves between states.

In Frames 1.4 and 1.5 the architecture for the Mealy and Moore FSMs were shown. In both cases, the memory elements shown are the flip-flops discussed in the previous paragraph.

At this stage it is perhaps worth while looking at a simple FSM design in detail to see what it looks like. This will bring together all the ideas discussed so far, as well as introducing a few new ones. However, try answering the following questions before moving on to test your understanding so far:

- Tasks 1. A Mealy FSM differs from a Moore FSM in .... (See Frames 1.4 and 1.5.)

- 2. The circles in a state diagram are used to.... (See Frames 1.8 and 1.9.)

- 3. Outside World Inputs are shown in a state diagram where? (See Frames 1.8 and 1.9.)

- 4. Outside World Outputs are shown in a state diagram where? (See Frame 1.9.)

- 5. The internal flip-flops in an FSM are used to . . . . (See Frame 1.10.)

Go to Frame 1.11

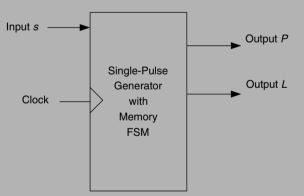

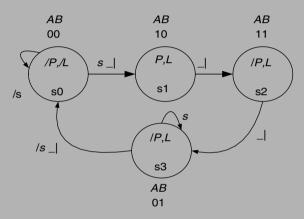

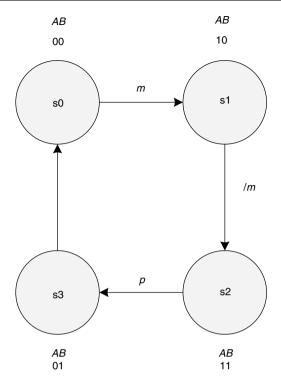

### Frame 1.11 Example of an FSM: a single-pulse generator circuit with memory

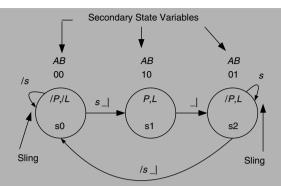

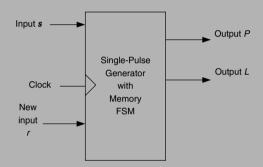

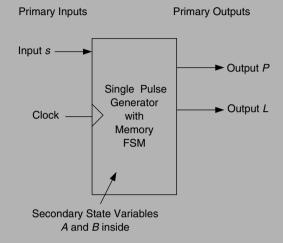

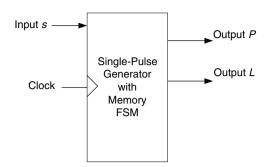

The idea here is to develop a circuit based on an FSM that will produce a single output pulse at its primary output P whenever its primary input s is taken to logic 1. In addition, a primary output L is to be set to logic 1 whenever input s is taken to logic 1, and cleared to logic 0 when the input s is released to logic 0. Output L acts as a memory indicator to indicate that a pulse has just been generated. The FSM is to be clock driven, so it also has an input clock. The block diagram of this circuit is shown in Figure 1.11.

Figure 1.11 Block diagram of single-pulse with memory FSM.

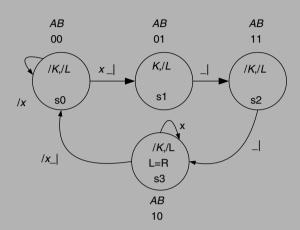

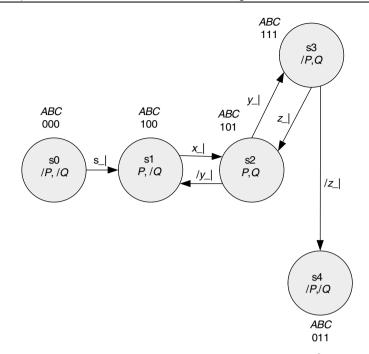

A suitable state diagram is shown in Figure 1.12.

In this state diagram the sling (loop going to and from s0) indicates that while input *s* is logic 0 (/*s*) the FSM will remain in state s0 regardless of how many clock pulses are applied to the FSM. Only when input *s* goes to logic 1 (*s*) will the FSM move from state s0 to s1, and then only when a clock pulse arrives. Once in state s1, the FSM will set its outputs *P* and *L* to logic 1, and on the next clock pulse the FSM will move from state s1 to state s2.

Figure 1.12 State diagram for single-pulse with memory FSM.

The reason why the FSM will stay in state s1 for only one clock pulse is because, in state s1, the transition from this state to state s2 occurs on a clock pulse only. Once the FSM arrives in state s2 it will remain there whilst input s = 1. As soon as the input s goes to logic 0 (/s) the FSM will move back to state s0 on the next clock pulse.

Since the FSM remains in state s1 for only a single clock pulse, and since P = 1 only in state s1, the FSM will produce a single output pulse. Note that the memory indicator *L* will remain at logic 1 until *s* is released, so providing the user with an indication that a pulse has been generated.

Note in the FSM state diagram (Figure 1.12) that each state has a unique state identity s0, s1, and s2.

Note also that each state has been allocated a unique combination of flip-flop states:

- state s0 uses the flip-flop combination A = 0, B = 0, i.e. both flip-flops reset;

- state s1 uses the flip-flop combination A = 1, B = 0, i.e. flip-flop A is set;

- state s2 uses the flip-flop combination A = 0, B = 1, i.e. flip-flop A is reset, flip-flop B is set.

The A and B flip-flops values are known as the secondary state variables.

The flip-flop outputs are seen to define each state. The *A* and *B* outputs of the two flip-flops could be used to determine the state of the FSM from the state of the *A* and *B* flip-flops. The code sequence shown in Figure 1.12 follow a none unit distance coding, since more than one flip-flop changes state in some transitions.

Go to Frame 1.12.

### Frame 1.12 The output signal states

It would also be possible to tell in which state the output *P* was to be logic 1, i.e. in state s1, where the flip-flop output logic levels are A = 1 and B = 0.

Therefore, the output  $P = A \cdot / B$  (where the middot is the logical AND operation). Note that the flip-flops are used to provide a unique identity for each state.

Similarly, output *L* is logic 1 in states s1 and s2 and, therefore, L = s1 + s2.

$L = s1 + s2 = A \cdot /B + /A \cdot B.$

Also, see that since each state can be defined in terms of the flip-flop output states, the outside-world outputs can also be defined in terms of the flip-flop output states since the outside-world's output states themselves are a function of the states (*P* is logic one in state s1, and state s1 is defined in terms of the flip-flop outputs  $A \cdot /B$ ).

L is defined by  $A \cdot /B + /A \cdot B$ .

The allocation of unique values of flip-flop outputs is rather an arbitrary process. In theory, any values can be used so long as each state has a unique combination. This means that one cannot have more than one state with the flip-flop values of say  $A \cdot /B$ .

In practice, it is common to assign flip-flop values so that the transition between each state involves only one flip-flop changing state. This is known as following a *unit distance pattern*. This has not been done in the example above because there are two flip-flop changes between states s1 and s2.

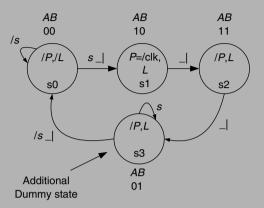

The single-pulse generator with memory state diagram could be made to follow a unit distance pattern by adding an extra state. This extra state could be inserted between states s2 and s0, having the same outputs for P and L as state s2.

Go to Frame 1.13.

### Frame 1.13

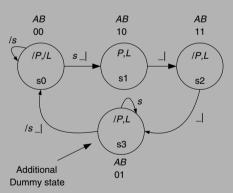

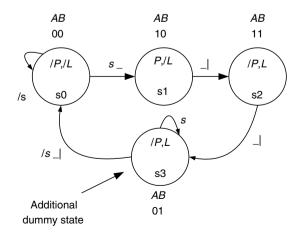

The completed state diagram with unit distance patterns for flip-flops is shown in Figure 1.13.

Figure 1.13 State diagram for single-pulse generator with memory.

Note that the added state has the unique name of s3 and the unique flip-flop assignment of A = 0 and B = 1. It also has the outputs P = 0, as it would be in state s0 (the state it is going to go to when s = 0). Also, L is retained at logic 1 until the input s is low, since L is the memory indicator and needs to be held high until the operator releases s.

In this design, the addition of the extra state has not added any more flip-flops to the design, since two flip-flops can have a maximum of  $2^2 = 4$  states (recall Frames 1.2 and 1.3).

The single pulse generator with memory FSM is to have an additional input added (called r) which will, when high (logic 1), cause the FSM to flash the P output at the clock rate. Whenever the r input is reverted to logic 0, the FSM will resume its single pulse with memory operation.

- *Tasks* 1. Draw the block diagram for the FSM.

- 2. Draw the state diagram for this modified FSM.

Go to Frame 1.14 to see the result.

### Frame 1.14

The block diagram is shown in Figure 1.14.

Figure 1.14 Block diagram for the FSM.

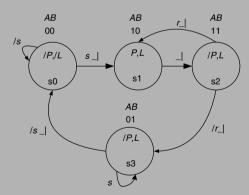

The new state diagram is shown in Figure 1.15.

Figure 1.15 Single-pulse generator with multi-pulse feature.

The additional input has been added and a new transition from s2 to s1. Note that, when r = 1, the FSM is clocked between states s1 and s2. This will continue until r = 0. In this condition, the *P* output will pulse on and off at the clock rate as long as input *r* is held at logic 1.

### An alternative way of expressing output L

In the state diagram of Figure 1.15,  $L = s1 + s2 + s3 = A \cdot /B + A \cdot B + /A \cdot B = A + /A \cdot B$ . Therefore, L = A + B. See Appendix A and the auxiliary rule for the method of how this Boolean equation is obtained.

An alternative way of expressing *L* is in terms of its low state:

$$L = /(\mathrm{s0}) = /(/A \cdot /B).$$

This implies that when A = 0 and B = 0, L = 0.

### Dealing with active-low signals

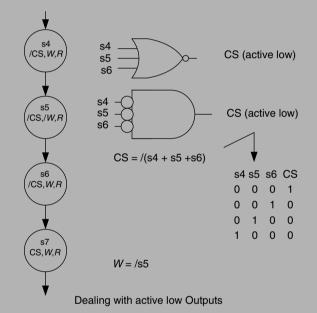

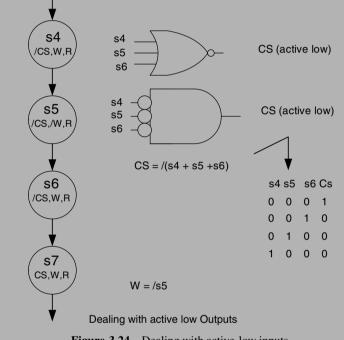

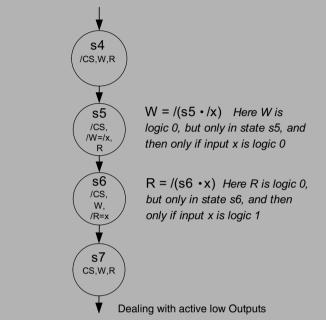

The state diagram fragment in Figure 1.16 illustrates how an *active-low signal* (in this case CS) that is low in states s4, s5 and s6 is obtained.

**Figure 1.16** Dealing with active-low outputs.

Also, the active-low signal *W* is obtained as well. From this it can be inferred that, to obtain the active-low output, all states in which the output is low must be negated. This is a common occurrence in FSMs and will be used quite often.

Finally:

- If an output is high in more states than it is low, then the active-low equation might produce a minimal result.

- If the output is low in more states than it is high, then the active-high form of the output equation will produce the more minimal result.

Go to Frame 1.15.

### Frame 1.15

The previous frames have considered the flip-flop output patterns. These are often referred to as the *secondary state variables* (Figure 1.17).

Figure 1.17 Block diagram showing secondary state variables in the FSM.

These are called secondary state variables because they are (from the FSM architecture viewpoint) internal to the FSM. Consider the Outside World inputs and outputs as being *primary*; then, it seems sensible to call the flip-flop outputs *secondary* state variables (state variables because they define the states of the state machine).

The outputs in the FSM are seen to be dependent upon the secondary state variables or flipflops internal to the FSM. Looking back to Frame 1.5, see that Moore FSM outputs are dependent upon the flip-flop outputs only. The Output Decoding logic in the single-pulse generator with memory example is

$$P = s1 = A \cdot /B$$

(see Frame 1.13) and

$$L = s1 + s2 + s3 = A \cdot / B + A \cdot B + / A \cdot B = A + / A \cdot B = A + B$$

(auxiliary rule again), i.e. it consists of one AND gate and an OR gate. This means that the single-pulse generator with memory design is a Moore FSM.

How could the single-pulse generator design be converted into a Mealy FSM?

One way would be to make the output *P* depend on the FSM being in state s1  $(A \cdot /B)$ , but also gate it with the clock *when it is low*. This would make the *P* output have a pulse width equal to the clock pulse, but only in state s1, and only when the clock is low. This would be providing a feed-forward path from the (clock) input to the *P* (output).

*Task* How could the state diagram be modified to do this?

Try modifying the state diagram, then go to Frame 1.16 to check the answer.

### Frame 1.16

The modified state diagram is shown in Figure 1.18.

Figure 1.18 State diagram with Mealy output P.

Notice that, now, the output P is only equal to logic 1 when

- the FSM is in state s1 where flip-flop outputs are A = 1 and B = 0;

- the clock signal is logic 0.

The FSM enters state s1, where the *P* output will only be equal to logic 1 when the clock is logic 0. The clock will be logic 1 when the FSM enters state s1 (0-to-1 transition); it will then go to logic 0 (whilst still in state s1) and P will go to logic 1. Then, when the clock goes back to logic 1, the FSM will move to state s2 and the flip-flop outputs will no longer be  $A \cdot /B$ , so the *P* output will go low again. Therefore, the *P* output will only be logic 1 for the time the clock is zero in state s1.

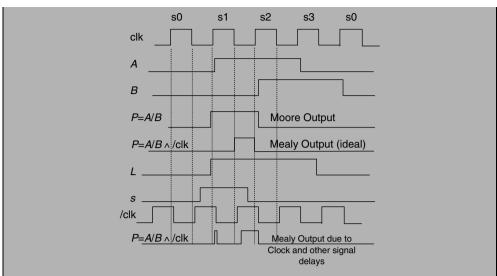

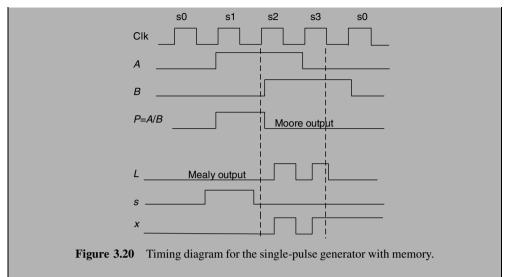

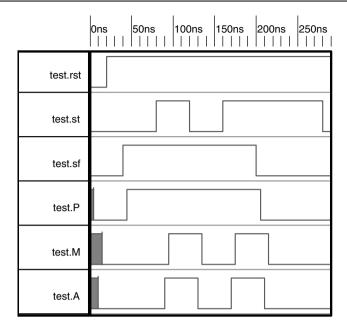

The timing diagram in Figure 1.19 illustrates this more clearly.

The waveforms show both versions of P (under the A and B waveforms in Figure 1.19). As can be seen, the Moore version raises P for the whole duration that the FSM is in state s1, whereas the Mealy version raises P for the time that the clock is low during state s1.

However, the bottom waveform for the Mealy *P* output illustrates what can happen as a result of a delay in the /clk signal, along with the change of state from s0 to s1(/A/B to A/B). Here, a glitch has been produced in the *P* signal as a result of the delay between clk and its complement /clk, after the *A* signal change. This is brought about by the clk signal causing *A* to change to logic 1 while the /clk signal is still at logic 1 due to the delay between the clk and / clk signals. This must be avoided.

This example is not unique; different delays can result in other unexpected outputs (glitches) from signal P. Essentially, if two signal changes occur, then a glitch can be produced in P as a result in the delays between signals (static 1 hazards).

Note that the P output signal is delayed in time as a result of the delays in signals A, B, and the /clk. This delay is not so important as long as it does not overrun the clock period (which in most practical cases it will not).

Figure 1.19 Timing diagram showing Moore and Mealy outputs.

It is best not to use the clock signal to create Mealy outputs. Also, as will be discussed in Chapter 3, it is wise, where possible, to use a unit distance coding for A and B variables to avoid two signal changes from occurring together; but more on this later. Now for another example.

*Task* Produce a state diagram for an FSM that will generate a 101 pattern in response to *m* going high. The input *m* must be returned low before another 101 pattern can be produced.

After attempting this task, go to Frame 1.17.

### Frame 1.17

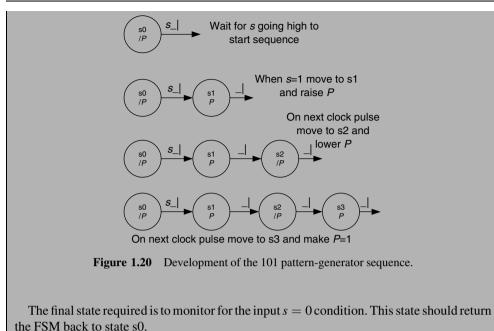

The solution to this problem is to use the basic arrangement of the single-pulse generator state diagram and insert more states to generate the required 101 pattern. This will be developed stage by stage so as to build up the complete design (Figure 1.20).

Start by first waiting for the input *s* to become logic 1. Therefore, in state s0, wait for s = 1. Once the input s = 1 and the clock changes 0 to 1, the FSM is required to move into the next state s1, where *P* will be raised to the logic 1 level.

The next state s2 will be used to generate the required logic 0 at the *P* output. And then the next state s3 will be needed to generate the last P = 1.

Note that the FSM must leave state s3 on a clock pulse so that P = 1 for the duration of a single clock pulse only.

*Task* Complete the FSM state diagram.

Now go to Frame 1.18.

### Frame 1.18

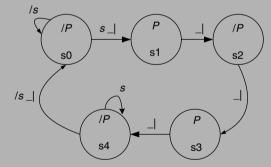

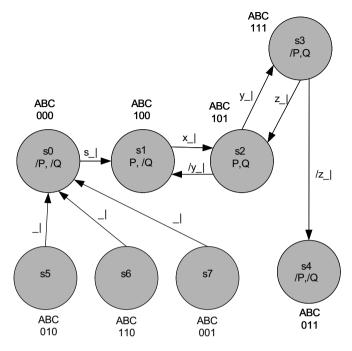

The completed state diagram is shown in Figure 1.21.

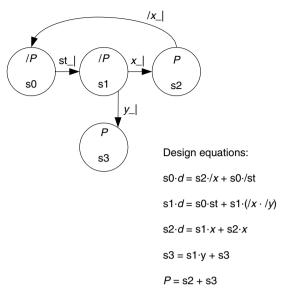

Figure 1.21 Complete state diagram for the 101 pattern-generator.

The Boolean equation for *P* in this diagram is P = s1 + s3. However, it is possible to make the *P* output a Mealy output that is only equal to one when in states s1 and s2, and only if an input y = 1. Then:

$P = s1 \cdot y + s3 \cdot y,$

since *P* must be high in both states s1 and s3, but only when the input *y* is high.

### A note on slings

A sling has been used for each state with an outside-world input along the transitional line. This is not really necessary, because slings are not used to obtain the circuits to perform the FSM function in modern state diagrams. In fact, they are really only included for cosmetic reasons, to improve the readability of the design. From now on, slings will only be used where they improve the readability of the state diagram.

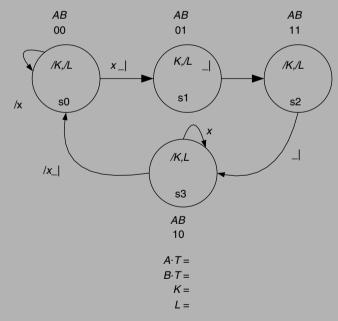

*Task* Now try modifying the state diagram to make it produce a 1010 sequence of clock pulses (in the same manner shown in Figure 1.21, but with the *P* output pulse in state s3 to be conditional on a new input called *x*. If x = 0, the FSM should produce the output sequence 1000 at *P*. If x = 1, then the output sequence at *P* should be 1010.

After drawing the state diagram, move to Frame 1.19.

### Frame 1.19

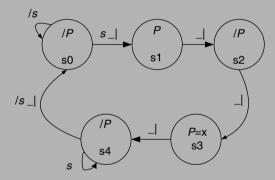

The modified state diagram is shown in Figure 1.22.

Figure 1.22 Modified state diagram with output *P* as a Mealy output.

In this state diagram, the input signal x is used as a qualifier in state s3 so that the output P is only logic 1 in this state when the clock is logic 1.

In state s3, the output P will only produce a pulse if the x input happens to be logic 1. A pulse will always be produced in state s1.

It can be seen that if x = 0, then when the input *s* is raised to logic 1, the FSM will produce the sequence 1000 at output *P*.

If x = 1, then when s is raised to logic 1, the FSM will produce a 1010 sequence at the output P. This FSM is an example of a Mealy FSM, since the output P is a function of both the state and the input x, i.e. the input x is fed forward to the output decoding logic. Therefore, the equation for P is

$P = s1 + s3 \cdot x.$

It would be easy to modify the FSM so that the 1000 sequence at *P* is produced if x = 1 and the 1010 sequence is produced if x = 0.

- *Tasks* 1. Produce the Boolean equation for *P* in state s3 that would satisfy this requirement.

- 2. Then, assign a unit distance code to the state diagram (refer to Frames 1.12 and 1.13 for why).

- 3. Finally, produce a timing diagram of the modified FSM.

After this, go to Frame 1.20.

### Frame 1.20

The answer to Task 1 in Frame 1.19 is as follows: the Boolean equation for *P* which will produce a *P* 1010 sequence when x = 0 is

$$P = s1 + s3 \cdot /x.$$

Note that in this case the qualifier for *P* is NOT *x*, rather than with *x*.

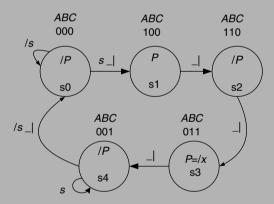

The answer to Task 2 in Frame 1.19, with regard to assigning a unit distance code to the state diagram, is shown in Figure 1.23.

Figure 1.23 State diagram with unit-distance coding of state variables.

The equation for P in s3 (it could be written outside the state circle if there is not enough room to show it inside the state circle) is conditional on the x input being logic 0. It is very likely that you will have come up with a different set of values for the secondary state assignments to those obtained here. This is perfectly all right, since there is no real preferred set of assignments, apart from trying to obtain a unit distance coding.

Some cheating has taken place here, since the transition between states s2 and s3 is not unit distance (since flip-flops *A* and *C* both change states). A unit distance coding could be obtained if an additional dummy state is added (as was the case in Frame 1.13 for the single-pulse generator with memory FSM).

However, in this example, one must be careful where one places the dummy state. If a dummy state is added between states s1 and s2, for example, then it would alter the *P* output sequence so that instead of producing, say, 1010, the sequence 10010 would be produced. A safe place to add a dummy state would be between states s3 and s4, or between states s4 and s0, since they are outside the 'critical' *P*-sequence-generating part of the state diagram. Move to Frame 1.21 for the timing waveform diagram solution.

### Frame 1.21

The answer to Task 3 in Frame 1.19 is as follows.

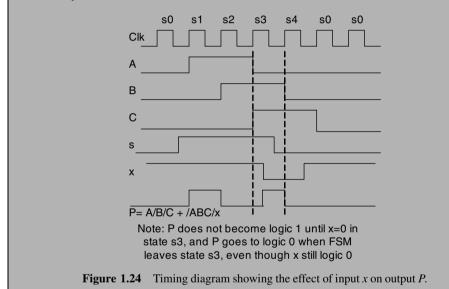

A solution is shown in Figure 1.24 based on the secondary state assignment that was used earlier, so your solution could well be different.

Note that in this solution the input x has been change to logic 0 in the middle of the clock pulse in state s3 just to illustrate the effect that this would have on the output P. Note that the output pulse on P is not a full clock high period in state s3.

*This is a very realistic event*, since the outside-world input *x* (indeed, any outside-world input) can occur at any time.

### 1.3 SUMMARY

At this point, the basics of what an FSM is and how a state diagram can be developed for a particular FSM design have been covered:

• how the outputs of the FSM depend upon the secondary state variables;

- that the secondary state variables can be assigned arbitrarily, but that following a unit distance code is good practice;

- a number of simple designs have shown how a Mealy or Moore FSM can be realized in the way in which the output equations are formed.

However, the state diagram needs to be realized as a circuit made up of logic gates and flipflops; this part of the development process is very much a mechanized activity, which will be covered in Chapter 3.

Chapter 2 will look at a number of FSM designs that control outside-world devices in an attempt to provide some feel for the design of state diagrams for FSMs. The pace will be quicker, as it will be assumed that the preceding work has been understood.

# 2 Using State Diagrams to Control External Hardware Subsystems

### 2.1 INTRODUCTION

In real-world problems there is often a need to use external subsystems, such as hardware timers/ counters, analogue-to-digital converters (ADCs), memory devices, and handshake signals to communicate with external devices.

This chapter looks at how a state diagram (and, hence, an FSM) can be used to control such devices. This opens up a much wider range of activities for the FSM and can lead to solutions in hardware that can be implemented in a relatively short time.

In later chapters, the ideas explored in this chapter will be used to develop some interesting real-world systems.

### 2.2 LEARNING MATERIAL

### Frame 2.1

One of the most common requirements in an FSM is the need to wait in a state for some predefined period. For example, a need to turn on an outside world output for a certain period of time, then turn it off again. This could be done by just allocating a number of consecutive states with the required output held high, but this would be very wasteful of states (and the corresponding flip-flops needed to implement the FSM) for all but very short delays. The best way of dealing with this kind of requirement is to use an external timer unit that can be controlled by the FSM.

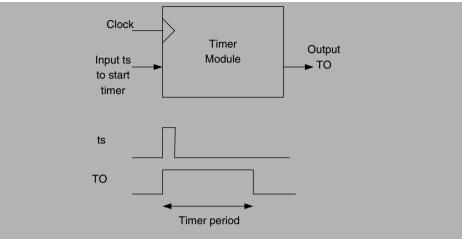

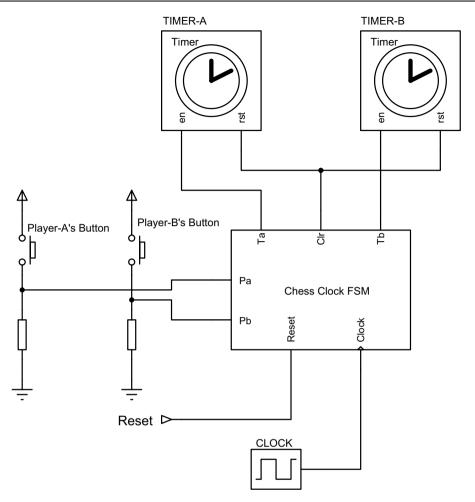

A typical timer unit might look something like the illustration in Figure 2.1.

The timer unit has two inputs, the clock input clk and the start timer input ts, and a single output TO. From the timing diagram (Figure 2.1) for this timer unit, the timer output TO will go high when the timer start input ts makes a 0-to-1 transition. The output TO will remain high until the time period has elapsed, after which it will go low.

$\odot$  2008 John Wiley & Sons, Ltd. ISBN: 978-0-470-06070-4

FSM-based Digital Design using Verilog HDL Peter Minns and Ian Elliott

24 Using State Diagrams to Control External Hardware Subsystems

Figure 2.1 Timing module.

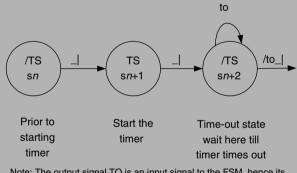

In Figure 2.2, TS, an output from the FSM, is used to start the timer prior to the time-out state. Then, on the next clock pulse the FSM moves into the time-out state. In the time-out state, the TS signal is returned low and the timer output signal 'to' is monitored by the FSM, which is looking for this 'to' signal going low, signalling the end of the timer period. At this point, the FSM will leave the time-out state.

Note: The output signal TO is an input signal to the FSM, hence its lower case name to.

Figure 2.2 State sequence to control the timing module.

Note that the FSM will wait in state sn + 2 until the signal 'to' goes low. Therefore, the time spent in state sn + 2 will be dictated by the timer unit.

Also note here that the timer output signal 'to' is in lower case now, since it is an input to the FSM, whereas the timer input signal TS is uppercase, since it is an output from the FSM.

Now please turn to Frame 2.2.

# Frame 2.2

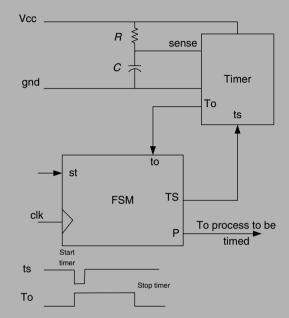

An example of how the timer unit could be used now follows.

Figure 2.3 Block diagram showing how to use the timing module.

In Figure 2.3, the FSM is controlling a timer unit. This timer unit happens to be a little different to the one seen in Frame 2.1 in that it does not have a clock input. It is in fact a timer based around an RC charging circuit (a practical device would be the 555 timer units that are readily available). This does not alter things in any way as far as the FSM is concerned. Note that the actual time delay would be given by

$$To = 1.1 \times C \times R.$$

if Timer is a 555 timer chip.

The start input St starts the FSM from state s0. The idea here is to turn on the process P for a period of time (dictated by the RC time constant of the timer unit), then turn it back off again.

Task Produce the state diagram to do this. Then go to Frame 2.3 for a solution.

### Frame 2.3

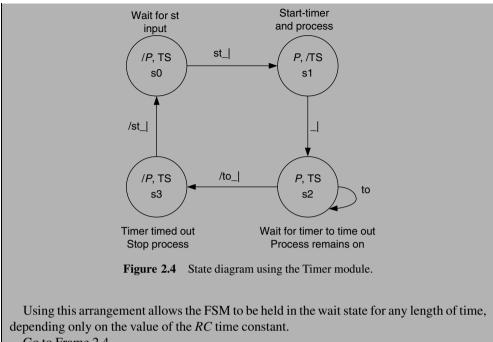

The state diagram to implement the arrangement shown in Figure 2.3 is shown in Figure 2.4. The process *P* is turned on in state s1, since the timer is started in this state, before the FSM moves into the time-out state s2. The FSM will remain in state s2 monitoring the timer output signal 'to' until the timer has timed out, and then move to state s3 to stop the process *P*.

Go to Frame 2.4.

# Frame 2.4

Having seen how to control an outside world device like a timer, the next stage is to see how other outside world devices can be controlled. This is really what FSMs are all about, controlling outside world devices.

Now look at how an FSM can be used to control

- an ADC;

- a memory device.

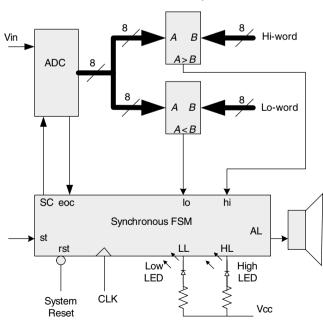

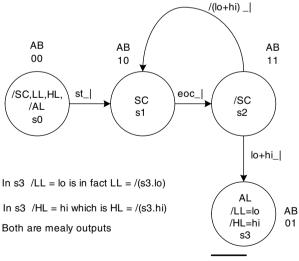

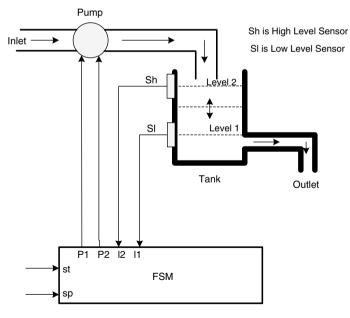

# **Controlling an ADC**

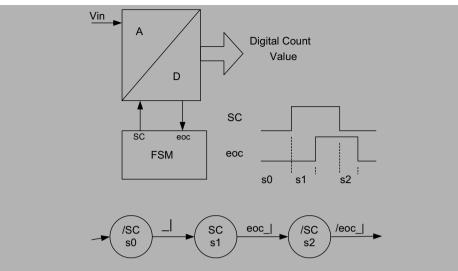

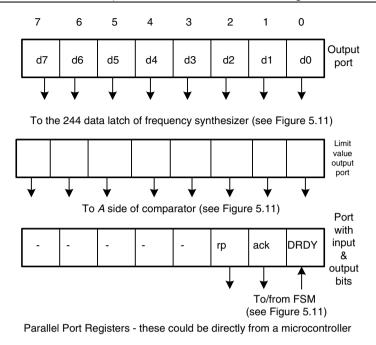

ADCs are used to convert analogue data into digital form. They are needed to allow digital computers to be able to process data from the real world (which is essentially analogue in nature). Most systems that use an ADC will be controlled from a microprocessor (or microcomputer). However, it is often the case that a system (or part of a system) will be implemented using a customized chip design, a programmable logic device (PLD), or even a field programmable logic array (FPGA). Consider the ADC shown in Figure 2.5.

This ADC has (as is usually the case) a Start Conversion input SC and an End Of Conversion output eoc.

Figure 2.5 Controlling an ADC from a state diagram.

The analogue input and digital outputs are connected to the external circuit and are not part of the FSM, since they form the *data flow* part of the system. The FSM is used to *control the system components* (the ADC in this case).

The segment of state diagram shows how the ADC is controlled by an FSM.

The FSM starts the ADC conversion in state s1 and waits for the  $eoc^1$  signal from the ADC to say that a digital value is available at the outputs of the ADC. At this point the FSM will move into state s2. Here, it will wait for eoc to return low before moving on to the next state.

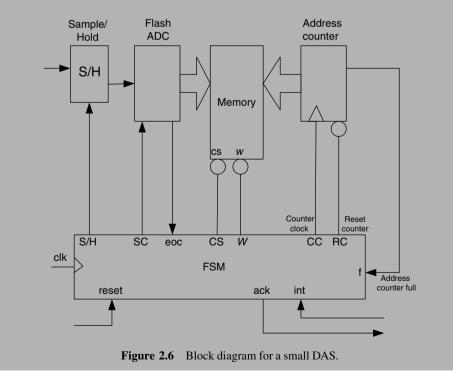

Now consider the small data acquisition system (DAS) shown in Figure 2.6. In this system there is an ADC and a number of other *outside world devices*. Go to Frame 2.5.

#### Frame 2.5

This particular example is a bit more complicated than the examples looked at so far; however, it can be separated out into more manageable parts, as will be revealed.

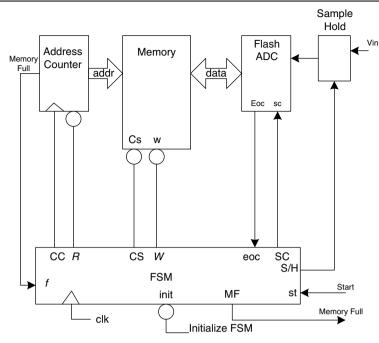

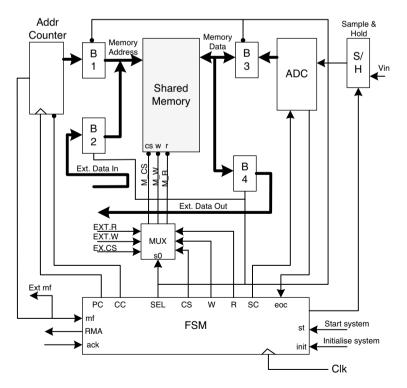

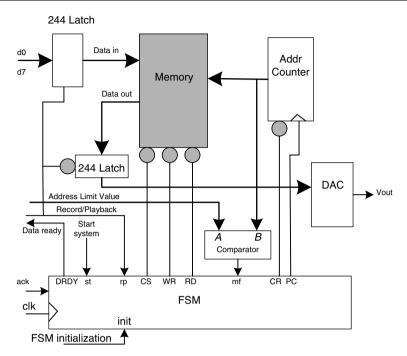

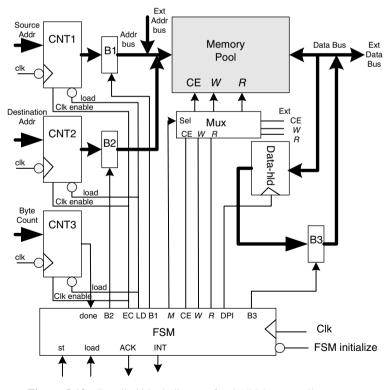

The diagram shown in Figure 2.6 uses the FSM to *control* a sample-and-hold (S/H) amplifier, ADC, a random access memory (RAM) device, and a simple binary counter.

All these outside world components allow the FSM to be able to

• sample a.c. analogue data from the outside world;

• store the data in RAM.

These could be under the control of a remote end device (which could be a microcomputer). Before attempting to produce a state diagram for this FSM, discussion is required on how an FSM can control the RAM and counter.

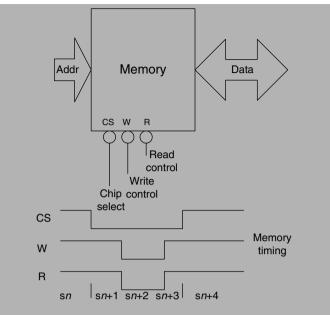

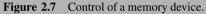

Consider Figure 2.7, which shows a memory device controlled by an FSM.

The memory device is written to/read from in sn+3 (on the rising edge of the read or write signal). Note that the memory device has a collection of address input lines (commonly called the address bus) and a set of data lines called the data bus. If the memory is read, only the data bus lines will be outputs. If the memory is a RAM, then the data bus lines will be bidirectional. This means that the /*R* and /*W* control signals can be used to condition the data bus lines to be either inputs (when/*W* is used) or outputs (when/*R* is used). In addition, there is a chip select input to select the memory chip.

#### Further information on memory device timing

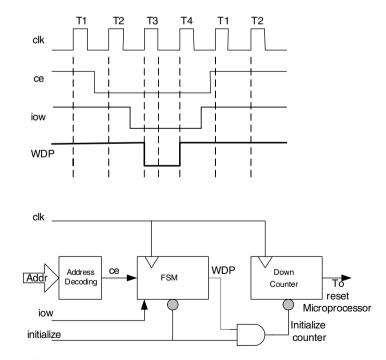

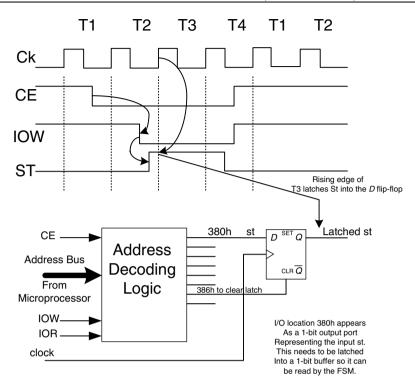

Figure 2.8 shows all the waveforms associated with a memory device.

The address bus selects a particular memory location at time T1 (the address bus lines changing just after the T1 starts). This causes the chip select CE signal to become active (low) at time T2 (allowing for propagation delays through the logic).

At time T3, the write signal *W* is activated (active low) and, as a result of this action, the memory chip data bus is taken out of its normal tri-state condition so it can accept input data.

<sup>&</sup>lt;sup>1</sup>Note that some ADCs have a busy signal instead of the eoc. These ADCs raise the busy signal when SC is asserted, lowering it when the conversion is complete.

At time T4 (after a suitable time has been allowed for the memory to settle) the write W signal is taken high, then the chip select signal CE will be taken high to deselect the memory chip. It is during this transition (0 to 1) of the W signal that the data are written into the memory chip. Note that in some memory chips the CE and W signals appear to go high in T4

Figure 2.8 Timing of the control of a memory device.

at the same time. The microprocessor will hold CE low long enough to allow the *W* signal to write the data into the memory device. This is usually because the propagation delay is longer in the CE path due to additional address decoding logic.

In a system controlled by an FSM, this can be done in the waveform diagram sequence, as shown earlier in this frame in Figure 2.7. However, an alternative arrangement could be to cause the CE signal to be delayed within the memory chip. This would be possible if the memory was being implemented in an HDL to be contained in an FPGA, perhaps also containing the FSM.

The main thing here is to ensure that the data can be written into the RAM before it is deselected.

*Note*: the signals CE and *W* need to be controlled by the FSM whenever the memory is to be written to or read from.

Note that if *W* is replaced by *R* then the memory cycle is a read memory cycle in which data stored in the memory chip will be output from the chip.

The read operation follows the same basic sequence as the write signal, and the arguments discussed earlier about delaying the chip select also apply.

Now go to Frame 2.6 to see how the memory chip can be controlled from an FSM.

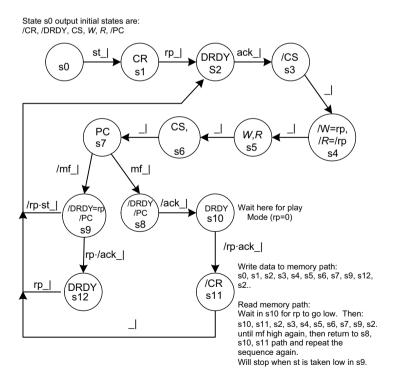

#### Frame 2.6

To access the memory device, the chip select line must be asserted (this means that the chip select line must be active, in this case active is logic 0). Then, write data into the RAM device by lowering the write signal line. A little later, raise the write line to logic 1 to write the data into the RAM device.

To read the contents of the RAM, first select the chip select line by making it go low, then a little time later set the read line low.

In most cases, 'chip select and read' or 'chip select and write' control lines can be raised high (to disassert them) at the same time. It is usually at this point in the cycle that the memory device is read or written; but, if there is a doubt about chip select remaining low long enough for the write or read operation to take place, then it is best to raise write or read first before raising the chip select signal.

In practice, the data bus will remain active for a few nanoseconds (typically 10 ns) in order for the data to be written or read by memory in memory controlled by a microprocessor, but in an FSM-controlled system the design engineer should ensure that this occurs either by adding another state to the state machine or by creating a delay on the chip select signal in the memory device.

The segment of timing diagrams of Figure 2.7 in Frame 2.5 illustrates this process.

When reading from and writing to memory devices, the process of reading and writing is implied to be from the point of view of the controlling device. The controlling device in a microprocessor system is the microprocessor. In our case, the controlling device is the FSM.

Task Try producing a segment of state diagram to control the memory device for writing.

Now go to Frame 2.7 to find out whether it is correct.

#### Frame 2.7

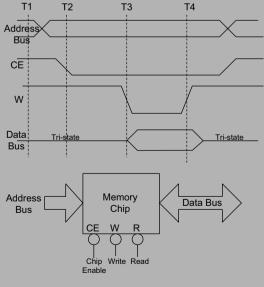

The segment of state diagram to control the memory illustrated in Frames 2.5 and 2.6 is illustrated in Figure 2.9.

Figure 2.9 Using an FSM to control the writing of data to a memory device.

In state sn, all controls are disasserted. In sn + 1 the chip select line CS is active; then, in state sn + 2, the write control line W is active. In state sn + 3, W is deactivated to write the data into the memory, and it is at this point that the data are written into the memory device. Finally, in state sn + 4, the chip select CS is raised to deselect the memory device.

To read or write to a memory device, the data transaction will occur in the memory element currently accessed by the address bus. To access another memory element, another address needs to be selected; this is done by the address counter. This is what the counter in Figure 2.6 (and in Figure 2.9) is being used for. In this case, each memory location is selected in sequence by incrementing the binary counter after accessing each memory location.

Note that in state sn + 5 the signal PC is set high. This increments the counter, thereby incrementing the address to point to the next consecutive memory location.

The counter can be reset to zero by sending the signal RC to logic 0. It can be incremented by the FSM with a pulse to the PC signal. In this way, each memory location of the memory can be accessed sequentially. Note that the address counter is incremented after disasserting the memory chip. This is because the address on the memory chip should not be changed while it is selected. Go to Frame 2.8.

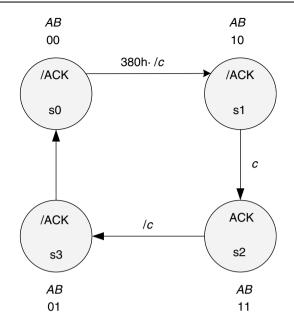

#### Frame 2.8

*Task* Having seen how the individual outside world devices are controlled in Figure 2.6, try to produce a state diagram to implement the FSM used to control the system.

The FSM is to wait in state s0 until it receives an interrupt signal from the remote end device over the int signal line. When this occurs, the FSM is to

- obtain a sample of data;

- perform an analogue-to-digital conversion;

- store the converted value into the memory device;

- increment the counter to point to the next available memory location.

The FSM should keep on doing this until the memory device is full. The FSM will know this when the f input (from the counter) goes high.

At this point, the FSM is to send an acknowledge signal to the remote end device using the ACK signal line; then, once the signal line int is low (remember, it was asserted high at the beginning of the sequence), it is to return to state s0 ready for another cycle.

When completed, go to Frame 2.9.

# Frame 2.9

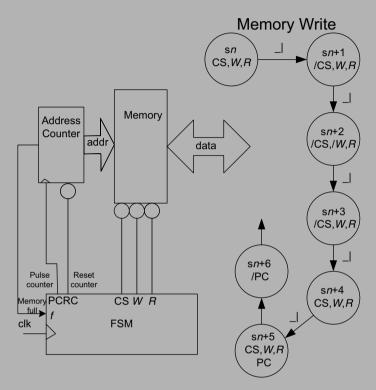

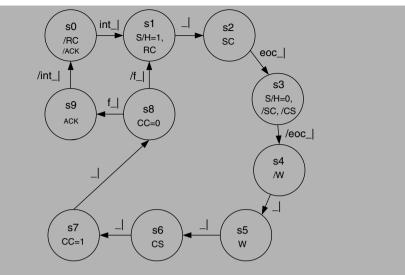

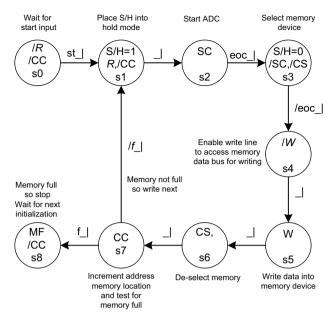

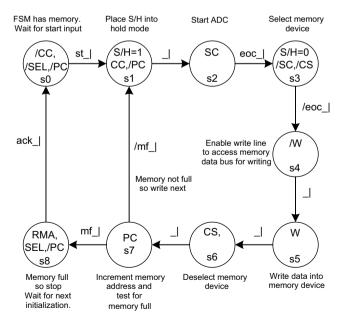

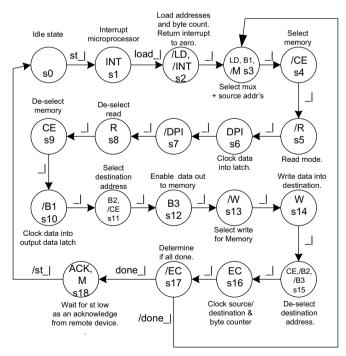

The complete state diagram is illustrated in Figure 2.10. Your state diagram may not look quite like this one, as there is more than one way of drawing a state diagram and there is no 'one' correct solution. However, the diagram in Figure 2.10 is very concise.

The first thing to note is that the reset line RC used to hold the memory address counter reset is held active (asserted) in state s0. Thereafter, it is held in its disasserted state (i.e. RC = 1). Not all states show this, but the sequential nature of the state diagram implies it.

When the int input is asserted, the FSM moves into state s1, removing the reset from the address counter and simultaneously asserting the sample-and-hold amplifier S/H = 1.

On the next clock pulse, the FSM moves to state s2, where (with the S/H still set) the start conversion signal of the ADC is asserted SC = 1. At this point, the FSM waits for the end of conversion signal eoc = 1; then, on the next clock pulse, it moves to state s3, where the S/H signal is disasserted (S/H = 0), since the ADC has converted the analogue data into digital form. While in state s3 the chip select in asserted (CS = 0) and the FSM waits in state s3 for eoc to be returned low. When this happens, on the next clock pulse the FSM moves to s4, where the memory device write signal line *W* is asserted low to set up the memory data bus lines as inputs. This allows the ADC digital output value to be input to the memory.

Figure 2.10 State diagram for the DAS.

The next clock pulse will move the FSM into state s5, where *W* is disasserted high, thereby writing the ADC value into the memory chip.

The FSM now moves into state s6 on the next clock pulse to deselect the memory (CS = 1). Go to Frame 2.10.

## Frame 2.10

At this stage in the FSM cycle, the FSM is in state s6.

The state machine will now move to state s7, where CC will be asserted high. On the next clock pulse, the state machine moves to s8, where CC will go low. The 0-to-1 transition on this signal line, caused by the FSM moving from state s6 to s7, will cause the address counter to increment. Note that, in state s6, the CS and W signals are now both high (disasserted).

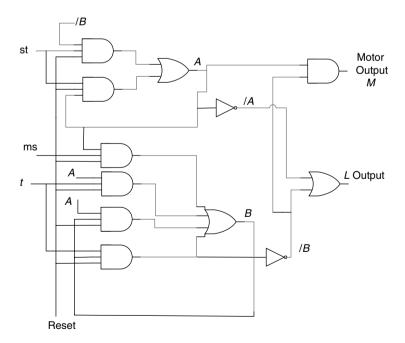

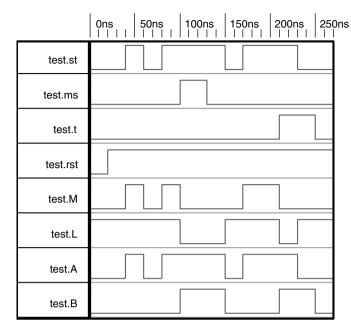

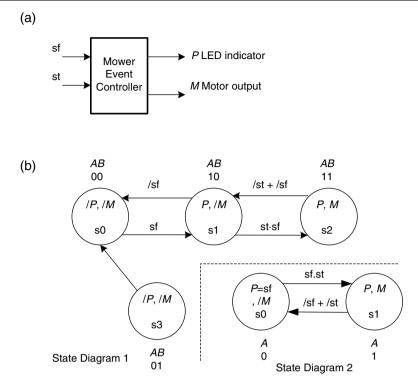

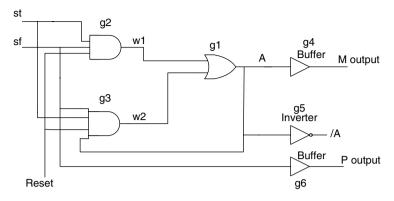

In state s8 the FSM can move, either to state s1, if the signal f is disasserted low (hence repeating the sequence s1 to s8), or, if signal f is asserted, the FSM can move from s8 into s9.