# Modeling and Simulation of High Efficient Symmetric Half-BridgeConverter (SHBC) for Server Switched Mode Power Supplies

#### Aneesha Jose, P.Swaminathan

Abstract—Asymmetric control scheme is an approach to achieve zero-voltage switching (ZVS) for half-bridge isolated dc-dc converters. But, it is not suited for wide range of input voltage due to the uneven voltage and current components stresses. Modeling and simulation of a new high-efficient symmetric half-bridge dc to dc converter is proposed in this paper. The proposed dc to dc converter regulates the output voltage by adjusting applied voltage on the main transformer with an auxiliary circuit while main switches are operated at both fixed duty ratio and switching frequency. So that, voltage stress on rectifier diodes and current stress on switches can be reduced.

Keywords- Symmetric Half-Bridge Converter (SHBC), Asymmetric Converter, Zero Voltage Switching (ZVS).

#### I. INTRODUCTION

The necessity of high-efficient server power system isemphasized in the medium power (600-800 W) supplies since the server infrastructure has spread to small companies these days [1]-[2]. In general, high frequency operation allows the use of small sized passive components in switch-mode power supplies (SMPS), through it causes the switching losses to increases in hard switching frequencies many soft switching techniques have been proposed, among them zero voltage transition technique is important. Several techniques have been proposed to reduce the switching losses and component stresses. Among the proposed techniques, the resonant reset forward converter[3], the conventional phaseshifted full-bridge (PSFB) converter[4]-[5], active-clamp forward converter[6]-[7] and the asymmetric control halfbridge converter are chosen as promising candidates for their zero voltage switching (ZVS) operation [8]-[10].Resonant reset-forward converter is a single ended switched mode converter with passive reset circuit. The major drawback of this type of the converter is that the voltage stress on the semiconductor devices is very high.

For medium power applications, the conventional phaseshift full-bridge (PSFB) dc to dc converter has more attention in descent decades due to its advantages such as' high conversion efficiency, high power density and lower electromagnetic interference (EMI).

#### Manuscript received on December, 2012

However, the usage of the PSFB converter is limited to medium power supplies since it adopts large number of main switches on the primary side. Active clamp forward converter has simple structure, it reduces voltage stress on the active switching elements thereby permitting the usage of low voltage rating devices, but it is also suffered from highvoltage rating of the main switch and degrades the performance of converters.

The asymmetric half bridge converter is the most attractive topology among the different topologies discussed earlier. The voltage across the switches in the Half-bridge is clamped to the input voltage, allowing the use of more efficient lower voltage MOSFETS. Lower voltage across the transformer primary allows a smaller number of primary turns. This result in lower leakage inductance, and makes the planar construction of the transformer easier. Also attains wide ZVS range. However, the asymmetric half-bridge converter also has the following drawbacks; The remained dc offset current at the magnetizing inductor decreases the transformer utilization, duty cycle restrictions are more severe in the asymmetric half bridge converter. Distribution of voltage stress between output rectifiers is more uneven in asymmetrical half bridge circuit than in other topologies. With the use of auxiliary transformer, converter extended its nominal duty ratio, but the offset problems of the magnetizing current are still remained in the transformers [11]. But power density and core utilization are severely deteriorated in the converter. Duty cycle shifted pulse width modulation control technique proposed is very simple and able to eliminate magnetizing current offset of the converter [12]. As a result, one of the two switches in the converter is still operated in hard switching condition, and large ripple current is produced in the rectifier.

#### II. HALF BRIDGE CONVERTER TOPOLOGY

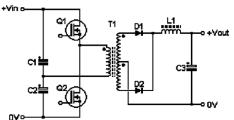

The half bridge converter is a buck derived topology operates in the step-down mode and the power is delivered from the source to the load[2]. This converter topology has gained popularity because of its simple soft switching simple controller designing as compared to other topologies, low volume and weight, and low cost due to less number of active and passive devices. The two mains capacitors C1 and C2 are connected in series. The two switches are driven alternately, and this will connects each capacitor across the single primary winding each half cycle. V/2 is superimposed symmetrically across the primary in a push-pull manner. Power is transferred to the output on each transistor conduction time and a

Aneesha Jose, Electrical and Electronics Engineering, Karunya University, Coimbatore, India.

**Prof. P.Swaminathan**, Electrical and Electronics Engineering, Karunya University, Coimbatore, India.

# Modeling And Simulation of High Efficient Symmetric Half-Bridge Converter(SHBC) for Server Switched Mode Power Supplies

maximum duty cycle of 90% is available. Since the primary is driven in directions, a full wave buck output filter (operating at twice the switching frequency) rather than a half wave filter is implemented.

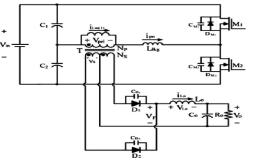

Fig. 1 Half bridge converter topology

There are two conventional control schemes for the half bridge DC-DC converter, symmetric control and asymmetric (complimentary) control. The main drawback of the symmetric control is that both primary switches in the converter operate at hard switching condition. Also, during the off-time period of two switches, oscillation between the transformer leakage inductance and junction capacitance of the switches results in energy dissipation and electromagnetic interface emissions due to reverse recovery of MOSFETs body diodes. To suppress the oscillation, resistive snubbers are usually added. So that, energy in the transformer leakage inductance is significantly dissipated in snubbers. Therefore, the symmetric-control of half bridge is not a good candidate for high switching frequency power conversion. Fig.2 shows the circuit diagram for asymmetric half bridge converter. The asymmetric control was proposed to achieve ZVS operation for HB switches. Two drive signals are complementarily generated and applied to high side and low side switches may be turned on at ZVS conditions owing to the fact that the transformer primary current charges and discharges the junction capacitance. But, asymmetric stresses distribution on the corresponding components may occur due to the asymmetric duty cycle distribution for the two primary switches are not identical and voltage and current stresses on secondary rectifiers with higher voltage rating are needed at the penalty of degrading the performance and efficiency of the rectifier stage.

To overcoming the all the drawbacks of asymmetric half bridge converter, a new high efficient symmetric half bridge dc to dc converter is proposed. In the symmetrical converters which always require an even number of switches, the full available flux swing in both quadrants of the B / H loop is used, thus utilizing the core much more effectively. Therefore symmetrical converters can produce more power than their asymmetrical converters.

Fig. 2 Asymmetric half bridge converter

# III. CIRCUIT DESCRIPTION OF THE SYMMETRIC DC-DC CONVERTER

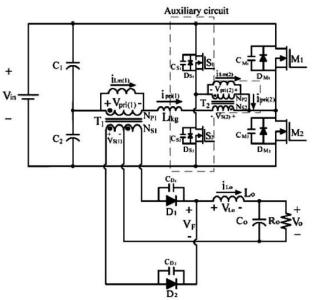

The proposed symmetric converter consists of an auxiliary circuit for the output regulation. An auxiliary circuit has two auxiliary switches and one auxiliary transformer. It can eliminates all the drawbacks of the asymmetric half bridge converter With the auxiliary transformer converter extended its nominal duty ratio, i.e. main switches can be operated in 50% duty ratio and fixed switching frequency.

Main switches always operated in 50% duty ratio, their ZVS operation are easily achieved. Employing auxiliary switches, transformer utilization is increased with no dc offset of magnetizing current. When input voltage decreases, the auxiliary transformer supplies additional voltage to the main transformer.

Fig. 3 shows a circuit diagram of the proposed symmetric dc/dc converter. It is based on the conventional asymmetric half-bridge converter, and the auxiliary circuit is composed on the primary side of the converter. The auxiliary circuit is consist of an auxiliary transformer (T2) and two auxiliary switches (S1 and S2). The output voltage is regulated by controlling the phase differences Deff between the main switches and auxiliary switches. When the supply voltage decreases, Deff is increased and additional voltage is provided to compensate the decreased input voltage. As the auxiliary circuit is used only for the regulation purposes, the magnetic size of the auxiliary transformer is much smaller than that of the main transformer, and the auxiliary transformer core loss is negligible at nominal operating condition

Fig. 3Proposedhalf bridge dc-dc converter

# IV. PRINCIPLE OF OPERATION

For the mode analysis of converter in steady state, several assumptions are made as follows.

- 1) The switches M1, M2, S1, and S2 are ideal components.

- 2) The capacitors C1 and C2 are considered as constant voltage sources, (1/2)Vin .

- 3) Turn ratio of the main transformer (T1) is n1 = NP 1 / NS 1and n2 = NP 2 / NS 2 for the auxiliary transformer (T2).

*Mode 1* : In mode 1 extra voltage is added to the nominal main transformer voltage for the regulation of the converter. Thus, the input capacitor voltage Vin /2 and reflected auxiliary transformer voltage, VS(2) were applied to the main transformer.

Mode 2: When auxiliary switch S1 is turned off, mode 2 begins. The output capacitors of the auxiliary switches CS 1 and CS 2 are charged and discharged, in a resonant manner. Since the large output inductor energy is participated in this resonance, the ZVS condition of auxiliary switches S1 and S2 are easily realized.

Mode 3: After the auxiliary switch S2 is completely discharged, the current of the auxiliary circuit flows through the body diode of S2. Thus, the voltage of S2 is sustained at zero volt, and the applied voltage to the main transformer remains at Vin /2.

Mode 4: When the auxiliary switch S2 is turned on, mode 4 begins. Since the output capacitor of S2 is completely discharged in the mode 3, it is turned on under ZVS condition.

Mode 5: The main switch M2 is turn off at the beginning of this mode. The voltage of the output capacitor of main transformer CM2 is linearly charged from 0 V, and the voltage of CM1 is linearly discharged from Vin at the same time by utilizing the large output inductance. This mode continues until the time when the primary voltage of the transformer reaches to 0 V.

*Mode* 6: When the main transformer voltage is decreased to 0 V, the voltage of main-switch M2 increases in manner of resonance between Llkg and CM1 + CM2.

Mode 7 : In mode 7, the primary current flows through the body diode of the main switch, M1 . As the main transformer is regarded as short circuit, all voltages in the circuit are applied to the leakage inductance and the primary current is sharply decreased.

Mode 8: When the main switch M1 is turned on, this mode begins. The primary current flowing though the body diode of M1 in the previous mode changes the path to the channel of switch M1.

#### SIMULATION OF PROPOSED SYMMETRIC V. **CONVERTER**

To verify the operation of the proposed converter and evaluate performance of the converter, simulation circuits have been designed with following specifications:

- Input voltage 400V

- Output voltage 12V

- Output power --700W

- Output current 58A

- Switching frequency 86kHz

The frequency of the output filter of the proposed converter is doubled and the applied voltage to the output inductor is also decreased. Output inductance required for the proposed symmetric converter is;

(1)

$$L_{o} = \frac{\frac{0.5V_{s} + V_{s} / (N_{s(2)} / N_{P(2)})}{(N_{s(1)} / N_{P(1)})} - V_{o}}{\Delta I_{o}} D_{a}T, \quad (0 < D_{a} < 0.5)$$

Output filter capacitance can be calculated using the equation;

.....(2)

Load of this converter circuit is taken as resistive load. The resistance value is calculated as:

...... (3)

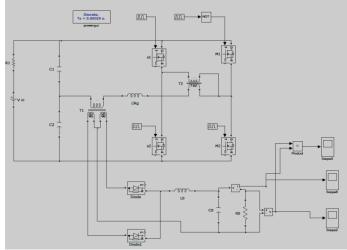

Simulation of the circuit is done with MATLAB 7.10(R2010a) /Simulink 7.10.

There are two main factors that will be considered for the selection of turn ratio of the transformers in the proposed symmetric converter.

These are the voltage regulation condition and the loss at the auxiliary circuit. the main transformer is always operated with its maximum duty ratio and output voltage is regulated by controlling the effective duty ratio of the auxiliary circuit.. When the input voltage decreases, the auxiliary circuit provides additional voltage to the main transformer for the compensation of the input voltage. So, to satisfy the regulation condition, the voltage provided by the auxiliary transformer must be able to increase as much as maximum input differences.

Fig.4. MATLAB/Simulink model of SHBC

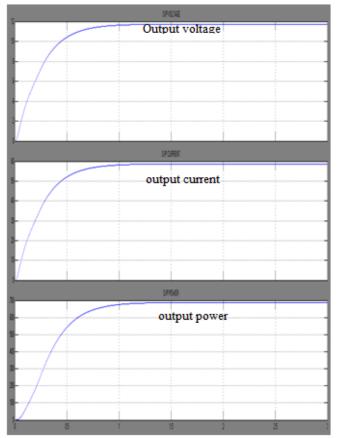

Simulation of the symmetric circuit provides constant dc output voltage, output current and output power.

## VI. ANALYSIS OF THE CONVERTER

#### A. Dc conversion ratio

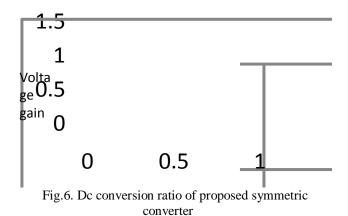

According to voltage-second balance rule of the output inductor, the dc conversion ratios is expressed as follows. whereDeff is effective duty ratio.

$$\frac{v_o}{v_{in}} =$$

(4)

The dc conversion ratio of the proposed symmetric converter shows linearity

#### B. dc offset current in magnetizing inductor

The switches of the proposed symmetric converter are controlled symmetrically, so the dc offset of the magnetizing current can be easily eliminated in this converter. So that, the transformer is fully utilized and it increases the power density of the converter system. The dc offset current for the proposed converter is expressed as follows: L

$$Deff(I_{LM}+I_o/n) = Deff(-I_{LM}+I_o/n)$$

(5)

# Modeling And Simulation of High Efficient Symmetric Half-Bridge Converter(SHBC) for Server Switched Mode Power Supplies

Fig.5. simulation results of Symmetric half bridge dc-dc converter.

#### C. Output filter inductor

The frequency of the output filter of the proposed converter is doubled and the applied voltage to the output inductor is decreased. Thus the required output inductance for the same ripple current condition can be reduced significantly in the proposed converter compared to that of the asymmetric halfbridge converter. This property willhelps to increase the power density of the system. The output inductor required for the proposed symmetric converter is expressed as;

$$\Rightarrow L_{o} = \frac{\frac{0.5V_{s} + V_{s} / (N_{S(2)} / N_{P(2)})}{(N_{S(1)} / N_{P(1)})} - V_{o}}{\Delta I_{o}} D_{a}T, \quad (0 < D_{a} < 0.5)$$

(6)

#### D. Component stresses

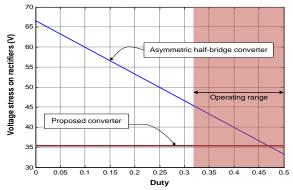

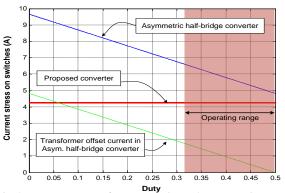

Because of the symmetric control of the switches, the proposed symmetric converter has balanced current and voltage stress on its components, but the asymmetric halfbridge converter has unbalanced stress distribution because of its asymmetric control method. As a result, the proposed symmetric converter can adopt primary switches with lower current ratings and rectifier diodes with lower voltage ratings than that of the asymmetric half-bridge converter. So that, the cost of the switches will be reduced, and the efficiency of the rectifier diodes is increased in the proposed converter.

Fig.7 voltage stress of asymmetric and symmetric converter Maximum voltage stress

Symmetric dc to dc converter - 36V Asymmetric half-bridge converter - 45V

Fig.8 current stress of asymmetric and symmetric converter

Maximum current stress Proposed converter - 4.2A Asymmetric half-bridge converter - 6.7A

## VII. CONCLUSION

A new symmetric half-bridge dc-dc converter simulated and analyzed. By employing one small auxiliary transformer and two small auxiliary switches, the proposed symmetric converter shows a good performance. It has low conduction loss and required smaller filter inductance. its symmetrical operation characteristic balances the voltage/current stresses on its components and eliminates the dc offset of magnetizing current, which reduces the utilization of the main transformer. Because of these good characteristics the proposed symmetric converter can be taken as a good candidate in middle power server system and industrial computers.

#### REFERENCES

- [1] In-Ho Cho.Kang-Hyun and Kyu-Min Cho," High efficient multilevel half-bridge converter" *IEEE Tans. Power Electron.*, vol.25,no.4.April.2010.

- [2] L. H. Mweene, C. A. Wright, and M. F. Schlecht, "A 1 kW 500 kHz front-end converter for a distributed power supply system," *IEEE Trans. Power Electron.*, vol. 6, no. 3, pp. 398–407, Jul. 1991.

- [3] Y. Gu, Z. Lu, L. Hang, Z. Qian, and G. Huang, "Three-level LLC series resonant DC/DC converter," *IEEE Trans. Power Electron.*, vol. 20, no. 4, pp. 781–789, Jul. 2005.

- [4] C. Zhao, X.Wu, P. Meng, and Z.Qian, "Optimum design consideration and implementation of a novel synchronous rectified soft-switched phase-shift full-bridge converter for low-outputvoltage high-output-current applications," *IEEE Trans. Power Electron.*, vol. 24, no. 2, pp. 388–397, Feb. 2009.

- [5] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, "Design considerations for high-voltage high-power full-bridge zerovoltageswitched PWM converter," in *Proc. Appl. Power Electron. Conf. Expo.*, 1990, pp. 275–284.

- [6] G. A. Karvelis, M. D.Manolarou, P. Malatestas, and S. N. Manias, "Analysis and design of non-dissipative active clamp for forward converters," in *Proc. IEE Proc. Elect. Power Appl.*, Sep. 2001, vol. 148, pp. 419–424.

- [7] Y. K. Lo and J.Y. Lin, "Active-clamping ZVS flyback converter employing two transformers," *IEEE Trans. Power Electron.*, vol. 22, no. 6, pp. 2416–2423, Nov. 2007.

- [8] P. Imbertson and N. Mohan, "Asymmetrical duty cycle permits zero switching loss in PWM circuits with no conduction loss penalty," *IEEE Trans. Ind. Appl.*, vol. 29, no. 1, pp. 121–125, Jan. 1993.

- [9] J. C. P. Liu, N. K. Poon, B. M. H. Pong, and C. K. Tse, "Low output ripple DC-DC converter based on an overlapping dual asymmetric half-bridge topology," *IEEE Trans. Ind. Appl.*, vol. 22, no. 5, pp. 1956–1963, Sep. 2007.

- [10] R. Miftakhutdinov, A. Nemchinov, V. Meleshin, and S. Fraidlin, "Modified asymmetrical ZVS half-bridge DC-DC converter," in *Proc. Appl. Power Electron. Conf. Expo.*, 2005, pp. 567–574.

- [11] H. Mao, J. Abu-Qanhouq, S. Luo, and I. Batarseh, "Zerovoltageswitching half-bridge DC-DC converter with modified PWM control method," *IEEE Trans. Power Electron.*, vol. 19, no. 4, pp. 947–958, Jul. 2004.

- [12] K. M. Cho, W. S. Oh, and G. W. Moon, "A new half-bridge converter without DC offset of magnetizing current," in *Proc. Int. Conf. Power Electron.*, 2007, pp. 147–149.

AneeshaJose, was born in Kearla. She received her B.Tech degree in Electrical and Electronics from MAHATMA GANDHI university, Kerala in 2011. She is currently doing her M.tech, Power Electronics and Drives in KARUNYA university, Coimbatore, Tamilnadu, INDIA

**Prof.P.Swaminathan**, BE-EEE, M.TECH.-HVE, MBA-HR,[PhD-HVDC],,He has obtained his Degrees from MADRAS University, SASTRA University, PERIYAR University and with ANNA University, Tamilnadu, INDIA. His work experience is TEN years in Industries and TWELVE years in Engineering Institutions. He has published research papers in national, international conferences and international journals. He is a member of MISTE, MIEEE, MIAENG. His research area includes HVDC, VSC-HVDC, FACTS, AC DRIVES and RENEWABLE ENERGY. Presently he is working with department of EEE in KARUNYA University, Coimbatore, Tamilnadu, INDIA.