# Design of a Soft-Switching Asymmetrical Half-Bridge Converter as Second Stage of an LED Driver for Street Lighting Application

Manuel Arias, *Member, IEEE*, Diego G. Lamar, *Member, IEEE*, Francisco F. Linera, *Member, IEEE*, Didier Balocco, Almadidi Aguissa Diallo, and Javier Sebastián, *Senior Member, IEEE*

Abstract—High-brightness LEDs are considered remarkable lighting devices due to their high reliability, chromatic variety, and increasing efficiency. As a result, a high number of solutions for supplying LED strings are emerging. One-stage solutions are cost-effective, but their efficiency is low because they have to fulfill several purposes with only one converter: power factor correction (PFC), galvanic isolation (in some cases), and current regulation. Two-stage and three-stage solutions have higher efficiency because each stage is optimized for only one or two tasks and they are the preferred options when supplying several strings at the same time. In this paper, a two-stage solution is proposed. The first stage is the well-known PFC boost converter. The second stage, on which this paper is focused, is the asymmetrical half bridge (AHB). Its design has been optimized based on the needs and characteristics of LED-based street lighting applications. The proposed transformer design (with asymmetrical secondary windings) minimizes the conduction losses while the model of the converter during the dead times optimizes their duration, reducing switching losses in the MOSFETs and diodes. Experimental results obtained with a 40-W prototype show an efficiency as high as 94.5% for this second stage and validate the proposed design procedure and model.

Index Terms—Asymmetrical half-bridge (AHB) dc-dc converter, complementary control half-bridge dc-dc converter, LED's driver, street lighting based on LEDs.

# I. INTRODUCTION

HIGH-BRIGHTNESS LEDs (HB-LED) are becoming more popular in lighting applications because of their increasing efficiency [1]. In fact, their theoretical maximum efficiency is higher than that of other devices such as gas discharge lamps or incandescent lamps. They also have other important advantages, such as high reliability, chromatic variety, etc. As a result, a high number of different ac–dc and dc–dc topologies have been proposed for supplying LED strings. The key

Manuscript received April 28, 2011; revised June 22, 2011; accepted July 30, 2011. Date of current version February 7, 2012. This work was supported in part by AEG Power Solutions B.V. under Project FUO-EM-002-10 and by the Spanish government under Project MICINN-10-CSD2009-00046. Recommended for publication by Associate Editor S. Williamson.

M. Arias, D. G. Lamar, F. F. Linera, and J. Sebastián are with the Electronic Power Supply Systems Group, Universidad de Oviedo, 33204 Gijón, Spain (e-mail: ariasmanuel@uniovi.es).

D. Balocco and A. Diallo are with AEG Power Solutions, 22300 Lannion, France.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPEL.2011.2164942

issues of these topologies are high reliability (which involves the absence of electrolytic capacitors), high efficiency, power factor correction (PFC) in ac–dc converters, and, in some cases, galvanic isolation. These topologies can be classified according to the number of stages in cascade: one, two, or three.

One-stage solutions [2]–[5] imply low-cost designs and only one energy conversion. Nevertheless, this also means that all tasks need to be satisfied with only one stage, what normally results in a considerable reduction in efficiency. In addition, PFC converters without electrolytic capacitors have a high output voltage ripple. Due to the nature of the load (i.e., LEDs), this means a considerable low-frequency current ripple that leads to flickering. These one-stage solutions are the most suitable option for LED-based replacement lamps [6], in which the converter size needs to be quite small.

Two-stage topologies [7] usually have a PFC converter as first stage and a second stage in charge of canceling the low-frequency ripple of the PFC converter and regulating the current provided to the LED string [8], [9]. The second stage also provides galvanic isolation when needed. The two-stage topology provides the highest efficiency, but as there are needed as many second stages as LED strings are supplied, this can raise the cost considerably, especially if the second stages need to provide galvanic isolation.

A possible option for reducing the cost is the integration of the two stages into only one [10], [11]. Although efficiency significantly decreases with this approach, cost and size are greatly reduced. It should be taken into account that this approach has the same problem as the conventional two-stage topology when the number of strings increases. A possible solution to this problem is using only one converter and equalizing the current through each string with a quasi-nondissipative technique [12]. However, in many of these topologies, the voltage of the energy storage capacitor may be very high, increasing the voltage stress in the rest of the components.

In the three-stage solutions [13], [14], each converter is optimized for just one task: PFC, galvanic isolation, and current regulation in each string. Hence, although three energy conversions are done, efficiency can still be quite high due to the optimization of each stage. Nevertheless, this approach only makes sense when galvanic isolation is needed while supplying two or more LED strings. Typically, the first stage is a boost converter for achieving PFC [15]–[17]. The second stage is in charge of providing the galvanic isolation and, in some cases, canceling the voltage ripple of the first stage. The first and the

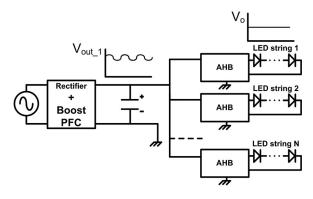

Fig. 1. Proposed topology.

second stages are common to all the LED strings, while there are as many third stages as LED strings supplied. In this way, the current provided to each string can be independently regulated. An example of this three-stage topology can be found in [13]. The first stage is a PFC boost converter operating in boundary conduction mode (BCM). The second stage is an LLC resonant converter that cancels the low-frequency ripple and provides galvanic isolation. The regulation of each LED string current is achieved by means of buck converters. As can be seen, the first and the second stages operate at variable frequency which may cause electromagnetic interference (EMI) problems and increase the difficulty of calculating the input EMI filter.

In this paper, a two-stage solution is proposed for LED-based street lighting applications. The main objectives of this topology are the achievement of high efficiency and high reliability while providing galvanic isolation. The second of these goals implies that the whole topology needs to be implemented without electrolytic capacitors. The first objective, achieving high efficiency, strongly determines the design of the second stage (on which this paper is focused). As can be seen in Fig. 1, the first stage is a boost converter common to all the LED strings and its purpose is achieving PFC. This topology has proven to be a perfect option for this kind of application, because it can be implemented without electrolytic capacitor and with an efficiency as high as 97%. The second stages (one for each LED string) are asymmetrical half bridges (AHBs) and they are in charge of providing the galvanic isolation and regulating the current supplied to the LED string (this topology is also known as complementary control HB). They also have to reduce the voltage ripple of the first stage, which is high due to the absence of electrolytic capacitors. It should be taken into account that this reduction is achieved by means of the closed-loop regulation, not by its output filter. In other words, its closed-loop regulator can be fast enough to reduce the low-frequency ripple. One of the main advantages of this converter is that it can achieve soft switching in primary switches. In addition, it is not a valid topology when the input voltage range is wide. Nevertheless, in this application, the average input voltage of the second stage is constant and the only voltage variation is due to the previously mentioned low-frequency ripple. The key issue in the design of this converter is reducing the losses. On the one hand, this topology has a transformer magnetizing current with an average

value that is not zero. This implies that the conduction losses in the transformer are higher than in traditionally controlled HB. Moreover, it is not possible to use Schottky diodes at the output because of the voltage levels demanded by LED strings (in the case of standard street lighting in Europe, around 150 V); hence, it is necessary to develop a method for reducing the switching losses of the ultrafast diodes that are going to be used (standard AHB only achieves soft switching in primary switches). These two points will be thoroughly analyzed in the paper, as they are the key issues for boosting the efficiency of the topology.

Because the final application of this LED driver is street lighting, some additional details should be taken into account. Wavelength (color) quality is less important than other issues such as cost and efficiency (including electricity-to-light conversion efficacy). Besides, the current stress on the LEDs should be the lowest as means to boosting the reliability, and indirectly, reducing the cost. These points can be achieved by means of, among other things, the amplitude-mode driving technique as it has lower current stress on LEDs and semiconductors than the PWM one.

The main advantages and disadvantages of this proposed topology compared to other topologies used in LED-based street lighting are:

- 1) High efficiency. Up to 94% in the second stage and 91% taking into account PFC boost + AHBs. The proposed topology also benefits from a high-efficacy electricity-to-light conversion due to the dimming technique employed [1].

- 2) Color quality. It is lower than it is with digital dimming but it is not a critical issue due to the final application (i.e., street lighting).

- 3) High reliability. It is high due to the absence of electrolytic capacitor and the use of amplitude-mode driving technique which reduces the current stress of the LEDs.

- 4) Constant switching frequency. The second stages of the proposed system operate at constant switching frequency. The first stage, the boost converter, can be implemented in two different ways. If it is implemented with SiC diodes, then it can be controlled by a standard controller base on the "multiplier approach" (i.e., UC3854) and it can operate in the continuous conduction mode (CCM). Of course, this means that the converter operates at constant switching frequency. In this case, high efficiency is due to the use of the aforementioned SiC diodes. On the other hand, high efficiency can also be achieved with ultrafast silicon diodes if the converter operates in BCM. In this case, the switching frequency is not constant, but the cost is considerably lower.

- 5) Galvanic isolation. It is provided by the proposed second stage. This requirement is sometimes necessary in order to comply with certain regulations or customer demands. Using galvanic isolated topologies in the second stage increases the size of the whole converter when the number of outputs is high. Nevertheless, in this design, size is not the key point as will be explained at the end of this section. The main issue is achieving high efficiency. If the galvanic isolation is provided by the second stages, the

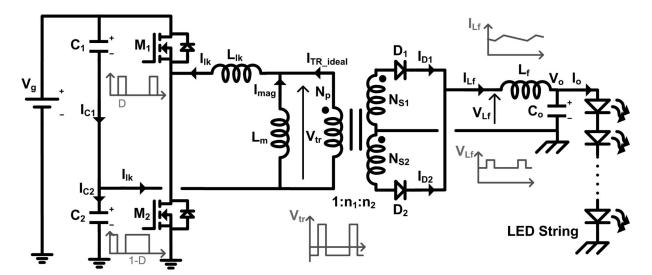

Fig. 2. Schematic of the proposed AHB.

first stage can be a boost converter in critical mode, which has an efficiency as high as 97%. Hence, if the number of independent outputs is low (2, 3, or 4) or even is a single output, the size is not significantly increased by achieving galvanic isolation in the second stage, but efficiency is considerably improved.

6) Smaller filter. The voltage at the output of the second-stage rectifier is easier to filter (see Fig. 2), and consequently, the necessary size of the filter is smaller. This is especially important since no electrolytic capacitors can be used.

It should be taken into account that size is not the key point in the design of the second stages due to the characteristics of the first stage. As electrolytic capacitors cannot be used, the size of the output capacitor of the first stage is going to be high because this converter is a PFC. Also, the size of this capacitor is not determined by the chosen switching frequency, but by the line frequency (in fact, twice the line frequency). Hence, the bulkiest stage is the first one and any size reduction in the second stages will not substantially affect the overall size of the LED driver.

This paper is organized as follows. Section II is focused on the steady-state analysis of the second stage, the AHB. Section III analyzes the minimization of the average value of the magnetizing current by means of the asymmetrical design of the transformer. Section IV describes the model of the converter during the dead time, which is useful for designing an AHB with reduced switching losses. Section V is a design guideline following all the previous explanations. Section VI describes the experimental results and Section VII provides the conclusions.

# II. AHB

The first stage of the proposed topology is a boost converter used in order to achieve PFC with high efficiency. The principle of operation of this kind of converter is very well known [18], [19].

For the proposed two-stage topology, the main issue is that implementing this boost converter without electrolytic capacitors implies a considerable low-frequency ripple at the output. This ripple is then determinant in the design of the second stages. The relative value of this peak-to-peak ripple will be denoted as  $r_v$  in this paper and is referred to the nominal output voltage  $V_g$ . Hence, the output voltage as a function of time can be expressed as

$$V_g = V_{g\_\text{nom}} \left( 1 + \frac{r_v}{2} \sin(2\omega_{\text{in}} t) \right) \tag{1}$$

where  $\omega_{\rm in}=2\pi f_{\rm in}$ ,  $f_{\rm in}$  is the line frequency, and  $V_{g\_{\rm nom}}$  is the nominal value of the first-stage output voltage. It should be taken into account that the ripple of the first stage will not affect the output voltage of the second stage because its closed-loop control can be fast enough to cancel this ripple.

The schematic of the AHB can be found in Fig. 2 [20]–[23]. As can be seen, it consists of an HB converter with their switches controlled with complementary signals (i.e., ideally, one of the two primary switches is always ON, different from what happens in standard HBs). The main consequence of this control technique is that due to the necessity of maintaining the volt–second balance in the transformer magnetizing inductor, the input capacitor voltages will vary according to the following equations

$$V_{C1} = (1 - D)V_q (2)$$

$$V_{C2} = DV_q \tag{3}$$

where  $V_{ci}$  is the voltage across each input capacitor, D is the duty cycle of  $S_1$ , and  $V_g$  is the input voltage of the AHB. It should be taken into account that in the AHB, D must always be lower than 0.5.

The output voltage will depend on the input voltage, the duty cycle, and the turns ratios of the transformer  $(n_1 = N_{s1}/N_p)$  and  $n_2 = N_{s2}/N_p$

$$V_o = n_1 V_{C1} D + n_2 V_{C2} (1 - D) = V_g D (1 - D) (n_1 + n_2).$$

(4

Analyzing the current balance in the primary side, it should be noted that the current through the leakage inductance satisfies the following equation

$$I_{\rm lk} = I_{C1} - I_{C2} = I_{\rm mag} + I_{\rm TR\_ideal}$$

(5)

where  $I_{\rm TR\_ideal}$  is the current through the ideal transformer,  $I_{\rm mag}$  is the current through the magnetizing inductor,  $I_{C1}$  and  $I_{C2}$  are the currents through the input capacitors  $C_1$  and  $C_2$ , and  $I_{\rm lk}$  is the current of the leakage inductance. The average value of  $I_{C1}$  and  $I_{C2}$  is zero because they are capacitor currents. Hence, in average value,  $I_{\rm mag}$  is equal to  $I_{\rm TR\_ideal}$  with different sign. Also, during DT, the current through the ideal transformer is equal to  $I_o n_1$ , while during (1-D)T, is equal to  $-I_o n_2$ . Considering this, the average value of the magnetizing current of the transformer is

$$\bar{I}_{\text{TR\_ideal}} = -\bar{I}_{\text{mag}} = -I_o[D(n_1 + n_2) - n_2].$$

(6)

As can be seen from (6), the average value of the magnetizing current is not necessarily zero, which is different from conventionally driven HBs. The main consequence of this average value is that the conduction losses of the transformer are going to be higher. Taking into account the low-power level that this converter will be driving (normally, LED strings are rated for 40–50 W), these losses imply a considerable reduction in efficiency. In Section III, the method employed for reducing this average value of the magnetizing current will be described. The basic idea involves using asymmetrical secondary windings in the transformer. This is different from the current design and results in a minimization of the average value of the magnetizing current.

A second important aspect regarding the AHB is the switching losses in MOSFETs and diodes. The switching losses of the MOSFETs can easily be reduced by employing the techniques that allow them to reach zero-voltage switching (ZVS). Nevertheless, these techniques usually use the energy stored in the leakage inductance. Due to the low value of the output current in LED-based applications (typically around 0.350 A), the value of the current through the leakage inductance is also low, and so is the energy stored in it. As a consequence, in this low-current application, it is not always possible to reach real ZVS and close-to-ZVS situations become acceptable. A possible solution is reducing the value of the magnetizing inductance. This leads to an increase of the magnetizing current ripple, and consequently, an increase in the amount of energy stored in the leakage inductance at the moment when the MOSFETs are switched. The application of this technique in this kind of converter will be analyzed in Section IV, since it is possible to reach ZVS even with low-current levels at the output. Regarding the switching process of the diodes, an important issue should be highlighted. Due to the voltage levels at the secondary side of the transformer, it is not possible to use Schottky diodes. Hence, switching losses become relevant as ultrafast diodes are used. As will be explained in Section IV, these switching losses are, in fact, the main factor of losses in this converter. In this section, the model of the converter during dead times will also be explained. This model will be used in Section V for designing an AHB with reduced switching losses not only in MOSFETs but also in diodes.

Apart from galvanic isolation, which is an important feature in order to comply with some regulations and/or customer requirements, another important advantage of the proposed topology is the size of the output filter. The voltage at the output of the AHB rectifier is easier to filter (see Fig. 2.). Hence, the size of the output inductor and/or the output capacitor can be smaller. This is especially important since electrolytic capacitors cannot be used.

### III. AVERAGE MAGNETIZING CURRENT MINIMIZATION

Normally, the analysis of the steady state of the AHB is done considering an equal number of turns in both secondary windings. Even when this is not considered as a design rule, such as in [24], the aim is different from reducing losses. In this section, the minimization of the average magnetizing current (and therefore, the conduction losses) will be analyzed.

As can be seen from (6), the average magnetizing current depends on the output current, the turn ratios of the transformer, and the duty cycle. Hence, for a given value of the output current, there is a linear relation between the magnetizing current and the duty cycle ( $n_1$  and  $n_2$  are fixed for a given AHB). Therefore, the minimum value of the average magnetizing current corresponds to the situation in which the duty cycle is maximum ( $D_{\rm max}$ )

$$\bar{I}_{\text{mag\_min}} = -I_o[D_{\text{max}}(n_1 + n_2) - n_2].$$

(7)

Also, the maximum average magnetizing current takes place when the duty cycle is minimum  $(D_{\min})$

$$\bar{I}_{\text{mag\_max}} = -I_o[D_{\text{min}}(n_1 + n_2) - n_2].$$

(8)

Therefore, the overall minimization of both values is achieved when they are equal in absolute value. This leads to the following condition

$$(D_{\max} + D_{\min}) = 2\frac{n_2}{(n_1 + n_2)}. (9)$$

This condition and the aforementioned linear relation imply that there is a duty cycle  $(D_{\rm Im0})$  for which the average value of the magnetizing current is zero

$$0 = I_0[D_{\text{Im}0}(n_1 + n_2) - n_2] \tag{10}$$

so

$$D_{\rm Im0} = \frac{n_2}{(n_1 + n_2)}. (11)$$

Considering (9) and (11),  $D_{\text{Im}0}$  can be expressed as

$$D_{\rm Im0} = \frac{D_{\rm min} + D_{\rm max}}{2} \tag{12}$$

which fixes the condition for minimizing the average value of the magnetizing current of the transformer. The required values for  $D_{\min}$  and  $D_{\max}$  are explained in Section V. The main consequence of this design method is that  $n_1$  and  $n_2$  are going to be different, as can be deduced from (11).

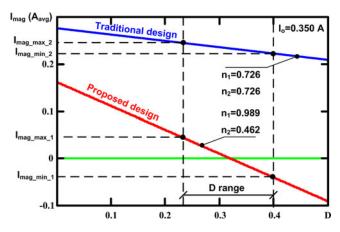

A graphical explanation can be found in Fig. 3. As can be seen, the average magnetizing currents of two different AHB

Fig. 3. Average magnetizing current for two different AHBs.

are plotted. The red line (proposed design) represents an AHB design taking into account (12). This is achieved by wisely choosing the values of  $n_1$  and  $n_2$  [see (11)]. The AHB that corresponds to the blue line follows a standard design in which  $n_1$  and  $n_2$  values are equal and do not satisfy (11) and (12). For both converters, the valid range of the duty cycle is [0.24, 0.4]. As can be seen, the maximum value of the average magnetizing current of the converter designed by observing (12) is equal to the minimum one in absolute value ( $I_{\text{mag}\_\text{max}\_1}$  and  $I_{\text{mag}\_\text{min}\_1}$ ). Nevertheless, when this equation is not considered (blue line), these minimum and maximum values are unbalanced ( $I_{\text{mag}\_\text{max}\_2}$  and  $I_{\text{mag}\_\text{min}\_2}$ ).

# IV. ZVS

As has been said, due to the low value of the nominal output current, ZVS is quite difficult to achieve in the AHB because the amount of energy stored in the leakage inductance is not high enough. Three options are possible in this situation:

- 1) Increasing the amount of energy stored in the leakage inductance by increasing the value of the magnetizing current;

- Increasing the amount of energy stored in the leakage inductance by increasing the value of the leakage inductance;

- 3) Accepting the closest situation to ZVS that can be achieved for the amount of energy that is stored in the leakage inductance without increasing either the magnetizing current or the leakage inductance.

The last option may be valid if high efficiency is not a primary concern. Nevertheless, in this application, the overall efficiency is very important and the switching losses have a great impact on it.

The second option, in a real design, leads to a high-size external inductor in series with the transformer. Besides, ZVS would not be achieved for the whole load range.

Therefore, in this kind of application it is necessary to increase the amount of energy stored in the leakage inductance by increasing the magnetizing current in the moment in which the switching processes take place. Nevertheless, it should be taken into account that this increment cannot be achieved by increas-

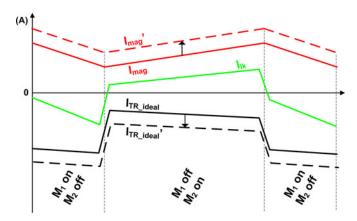

Fig. 4. Leakage inductance current for two different conditions of the average magnetizing current.

ing the average value of the magnetizing current. As can be seen in Fig. 4, the aforementioned increase of the average value of the magnetizing current does not affect the average value of the leakage current (equal to zero as has been explained previously) and, therefore, does not make easier or more difficult to achieve ZVS. Hence, reducing the average value of  $I_{\rm mag}$  reduces the conduction losses of the transformer but without affecting the ZVS of MOSFETs.

The best option for increasing the magnetizing current in the right instants (i.e., switching instants) is reducing the value of the magnetizing inductance. In this way, the ripple of  $I_{\rm mag}$  increases, and so does the energy stored in the leakage inductance  $L_{\rm lk}$  when the MOSFETs are going to be switched. This also increments the rms value of the current, and consequently, the conduction losses in the transformer and the MOSFETs. Nevertheless, the increment of the conduction losses is less significant than the decrease in the switching losses. The calculation of the necessary transformer magnetizing inductance will be carried out later in this section.

Although the switching losses in the MOSFETs before the aforementioned reduction were relevant, in this kind of application, the most critical issue is the switching losses in the diodes. Due to the value of the output voltage (in the case of standard street lighting in Europe, around 150 V), it is not possible to use silicon Schottky diodes, and therefore, ultrafast ones must be used. Hence, it is necessary to wisely analyze their switching process in order to assure that MOSFETs are not switched before the diodes have naturally turned OFF and ON. In this way, switching losses in the four switches (MOSFETs and diodes) are considerably reduced and efficiency is increased. First of all, it should be taken into account that the switching process of the diodes is related to the switching process of the MOSFETs. Hence, in the next sections, the behavior of currents and voltages across diodes and MOSFETs is described during the switching dead time. In this way, the equations that describe this dead time will help in the design of the proposed AHB. Some considerations are determined in this analysis:

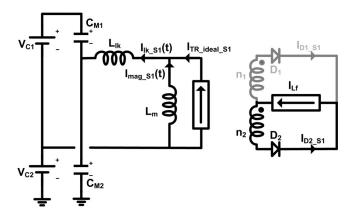

1) The voltages of the input capacitors ( $C_1$  and  $C_2$ ) are considered constant so that they will be represented as voltage sources  $V_{C1}$  and  $V_{C2}$  in Figs. 5–7.

Fig. 5. Equivalent circuit of the AHB during the first stage.

- The current through the output inductor can be considered constant during the switching dead time.

- 3) The value of the leakage inductance  $L_{lk}$  is considerably lower than the value of the magnetizing inductance  $L_m$ .

The dead time can be divided into three different stages. For the sake of simplicity, only the dead time between  $M_2$  turned OFF and  $M_1$  turned ON is going to be analyzed. Nevertheless, similar equations can be obtained for the other dead-time transient response (i.e., when  $M_1$  is turned OFF and  $M_2$  is turned ON).

### A. First Stage

The beginning of this first stage takes place when the MOS-FET  $M_2$  is turned OFF and the equivalent circuit for describing the operation is the one shown in Fig. 5. The primary side of the ideal transformer can be modeled as a current source  $(I_{\text{TR\_ideal }S1})$ . This source can be considered constant due to the high value of the output inductor and the short duration of the dead time, but the ripple in the output–inductor current should be taken into account. Hence, its constant value referred to the transformer's primary side can be expressed as

$I_{\mathrm{T\,R}\,\_\mathrm{id\,eal}\,\_S\,1}$

$$= \max \left[ 0, \left( I_o - \frac{V_g D \times (1 - D) \times (n_1 + n_2) - V_g D n_2}{2L_f} \times \frac{1 - D}{f} \right) n_2 \right]$$

(13)

where  $L_f$  is the value of the output filter inductor, f is the switching frequency of the AHB, and  $I_0$  is the output current. As the discontinuous conduction mode (DCM) may take place, negative values are not possible and the maximum function is introduced to obtain a general expression for both CCM and DCM.

The output current, considering the characteristic of the load (i.e., LED string) and (4), can be expressed as

$$I_o = \max \left[ 0, \frac{V_g D \times (1 - D) \times (n_1 + n_2) - V_{\gamma \perp \text{LED}} N}{R_{\text{LED}} N} \right]$$

(14)

where  $V_{\gamma \perp \rm LED}$  is the knee voltage of one LED diode, N the number of LEDs in the string, and  $R_{\rm LED}$  the dynamic resistance of a single LED. Obviously, negative current is not possible in this kind of load and the maximum function is again necessary.

Considering the circuit in Fig. 5, the equation that defines the voltage  $V_{CM\,2\_S1}$  across the parasitic capacitance of MOSFET  $M_2$  ( $C_{M\,2}$ ) during this stage is

$$V_{CM2\_S1}(t) = V_g D - V_g D \cos(\omega t)$$

$$+ \left(I_{TR\_ideal} + \frac{1}{2L_m} \times V_g D \times \frac{1 - D}{f}\right)$$

$$- I_o[D(n_1 + n_2) - n_2] L_T \omega \sin(\omega t) \quad (15)$$

where  $L_m$  is the value of the magnetizing inductance,  $L_T$  is the value of  $L_m$  plus the value of the leakage inductance  $L_{lk}$ ; and  $\omega$  is

$$\omega = \frac{1}{\sqrt{L_T C_T}} \tag{16}$$

where  $C_T$  is the sum of the two MOSFET parasitic capacitances  $C_{M1}$  and  $C_{M2}$ .

In (15), the second addend takes into account the current of the ideal transformer, the ripple of the magnetizing current, and its average value. If the average magnetizing current has been minimized, as explained in the previous section, it can be disregarded

$$V_{CM2\_S1}(t) = V_g D - V_g D \cos(\omega t) + \left(I_{TR\_ideal} + \frac{1}{2L_m} \times V_g D \times \frac{1-D}{f}\right) L_T \omega \sin(\omega t).$$

(17)

The end of this stage takes place when the voltage across the ideal transformer is zero, which means that the voltage across the magnetizing inductor is zero. In that moment, the voltage of the secondary windings is zero and the diodes change their situation: diode  $D_2$  is going to be turned OFF, while  $D_1$  is going to be turned ON. Considering that  $L_T$  is nearly equal to  $L_m$  (due to the low value of  $L_{lk}$ ), the end of this stage can be obtained by finding the instant in which the input voltage of the real transformer is zero (i.e.,  $V_{CM2-S1}$  is equal to  $V_{C2}$ )

$$V_g D \cos(\omega t_1) - \left(I_{\text{TR\_ideal}} + \frac{1}{2L_m} \times V_g D \times \frac{1 - D}{f}\right) \times L_T \omega \sin(\omega t_1) = 0. \quad (18)$$

All the parameters are known in (18) except  $t_1$ , which is the end of the first stage of the dead time.

For the next step, the current through the leakage inductance at the end of this step  $[I_{lk}\_S_1(t_1)]$  is going to be needed as an initial condition for the differential equation

$$I_{lk\_S1}(t_1) = V_g D\omega C_T \sin(\omega t_1) + \left(I_{TR\_ideal} + \frac{1}{2L_m} \times V_g D \times \frac{1-D}{f}\right) \cos(\omega t_1). \quad (19)$$

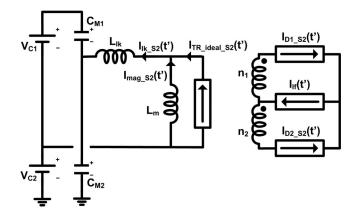

Fig. 6. Equivalent circuit during the second stage.

### B. Second Stage

In the second stage (see Fig. 6), the current source is no longer constant and the switching process of the diodes needs to be analyzed.

At the beginning of this second stage, diode  $D_2$  has begun the turning-OFF, while  $D_1$  has begun the turning-ON. This means that the current through diode  $D_2$  is going to be negative and equal to its reverse recovery current. Considering that the current through the output inductor is constant, the current through  $D_1$   $[I_{D1}(t')]$  can be expressed as

$$I_{D1\_S2}(t') = \max \left[ 0, \left( I_0 - \frac{V_g D \times (1 - D) \times (n_1 + n_2) - V_g D n_2}{2L_f} \times \frac{1 - D}{f} \right) \right] - I_{D2\_S2}(t') \quad (20)$$

where  $I_{D2\_S2}(t')$  is the current through  $D_2$  and t' is the time referred to  $t_1$  (i.e.,  $t' = t - t_1$ ).

Hence, the current through the ideal transformer is

$$I_{\text{TR\_ideal\_}S2}(t') = -\left[\max\left[0, \left(I_0 - \frac{V_g D \times (1-D) \times (n_1 + n_2) - V_g D n_2}{2L_f} \times \frac{1-D}{f}\right)\right] - I_{D2\_S2}(t')\right] n_1 + I_{D2\_S2}(t') n_2.$$

(21)

Although it has an exponential behavior, the reverse recovery current of a diode can be modeled with a linear equation

$$I_{D2\_S2}(t') = -I_{pk} + \frac{I_{pk}}{t_{rr}}t'$$

(22)

where  $I_{\rm pk}$  is the reverse peak current and  $t_{\rm rr}$  is the reverse recovery time of the diode  $D_2$ . These two parameters should be obtained from experimental data or from the datasheet, as they will strongly depend on  $I_o$ ,  $V_g$ , D, etc.

The values of  $L_M$  and  $L_f$  are considerably higher than  $L_{lk}$ , and as a consequence, any sudden variation of the current in the secondary windings (such as the reverse recovery current)

will mainly affect the current of the leakage inductance after a very short transient period that is disregarded in this analysis. Hence, considering this and (14), (21), and (22), the initial current through the leakage inductance in this second stage (t' = 0) is

$$I_{lk\_S2}(0) = I_{lk\_S1}(t_1)$$

$$-\left[\max\left[0, \left(I_0 - \frac{V_g D \times (1-D) \times (n_1 + n_2) - V_g D n_2}{2L_f} \times \frac{1-D}{f}\right)\right] + I_{pk}\right](n_1 + n_2). (23)$$

As can be seen from this equation, the initial value (after a very short transient period) of the leakage inductance at the beginning of the second stage is equal to the value of its current at the end of the first stage minus a factor that depends on the reverse peak current of  $D_2$  and the current of the output inductor.

The equations that define this second stage are

$$V_{CM2\_S2}(t') = V_g D - \frac{L_m \times (n_1 + n_2) \times I_{pk}}{t_{rr}} \times \cos(\omega t)$$

$$+ L_T \omega I_{lk\_S2}(0) \sin(\omega t')$$

$$+ L_m \times (n_1 + n_2) \times \frac{I_{pk}}{t_{rr}}$$

$$I_{lk\_S2}(t') = \frac{L_m \times (n_1 + n_2)I_{pk}}{L_T \times t_{rr} \times \omega} \times \sin(\omega t)$$

$$+ I_{lk\_S2}(0) \sin(\omega t'). \tag{25}$$

The time needed by the parasitic capacitor of  $M_2$  to be completely charged can be calculated with (24)

$$0 = V_g(D - 1) - \frac{L_m \times (n_1 + n_2)I_{\text{pk}}}{t_{\text{rr}}} \times \cos(\omega t'_{2\_{\text{aux}}}) + L_T \omega I_{\text{lk}\_S2}(0) \sin(\omega t'_{2\_{\text{aux}}}) + L_m \times (n_1 + n_2) \times \frac{I_{\text{pk}}}{t_{\text{rr}}}.$$

(26)

The duration of this second stage is not always equal to  $t'_{2\_aux}$ . It is necessary to compare this time with  $t_{rr}$ . If it is shorter, parasitic capacitor  $M_2$  will be fully charged and ZVS will be achieved if MOSFET  $M_1$  is turned ON. Nevertheless, if  $t'_{2\_aux}$  is longer than  $t_{rr}$ , ZVS has not been achieved and a third stage needs to be analyzed

$$t_2' = \min(t_{2,\text{aux}}', t_{\text{rr}}).$$

(27)

A very important issue of this stage is that the variation of the voltage applied by the secondary windings to the diodes is slow in comparison to the situation in which  $M_1$  is turned ON and  $(n_1 + n_2) \times (1 - D) \times V_g$  is directly applied to the reverse-biased diode. Hence, the reverse peak current is going to be small, and therefore, the di/dt of the current is going to be small as well. As a consequence, the reverse recovery time  $(t_{\rm rr})$  is going to be longer, as can be deduced from [25] and [26] or the datasheet of any diode. Although it is longer, the reduction in the reverse recovery current is considerable, and as a consequence, losses in

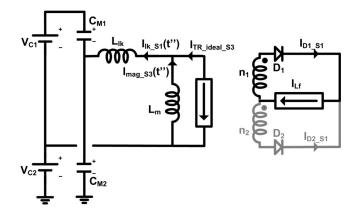

Fig. 7. Equivalent circuit during the third stage.

diodes are reduced. The precise variation of  $t_{\rm rr}$ ,  $I_{\rm pk}$ , and di/dt for different operating conditions of this converter is quite difficult to predict. Datasheets only provide part of the information and not for so low values of the diode voltage. Hence, two options are possible:

- Developing a mathematical expression as a result of experimental data.

- 2) Considering the same values of these variables for any valid operating condition of the converter. These values should reflect the worst possible situation (i.e., highest  $I_{\rm pk}$ , etc.)

# C. Third Stage

In this final stage, the conditions are similar to the first stage (see Fig. 7). Only one diode is turned ON  $(D_1)$ , while the other is turned OFF  $(D_2)$ . The only difference, apart from the initial conditions, is that the current of the output inductor referred to the primary side of the transformer has different sign in this third stage.

The equation of the parasitic capacitor voltage for this stage is

$$V_{CM2\_S3}(t'') = V_g D - [V_g D - V_{CM2\_S2}(t'_2)] \cos(\omega t'') + L_T \omega I_{lk\_S2}(t'_2) \sin(\omega t'').$$

(28)

This stage ends when the voltage of this capacitor is equal to  $V_g$  or when it reaches a maximum lower than  $V_g$  (in this case, ZVS would be impossible to achieve). It should be taken into account that under certain circumstances, this voltage is reached in the second stage. The time  $(t_3'')$  for this to happen can be calculated from (28) as follows:

$$0 = V_g (D - 1) - [V_g D - V_{CM2\_S2}(t_2')] \cos(\omega t_3'') + L_T \omega I_{lk\_S2}(t_2') \sin(\omega t_3'').$$

(29)

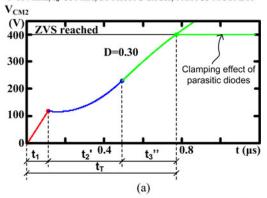

# D. Overall Analysis

Considering the three stages, (18), (26), and (29) allow us to calculate the minimum time needed by a certain AHB to reach ZVS in its MOSFETs, taking into account how the rectifier

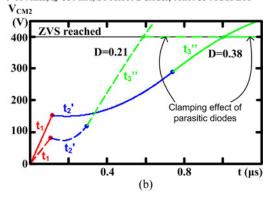

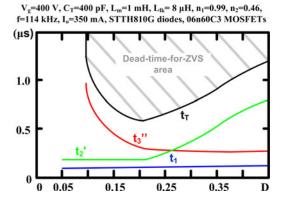

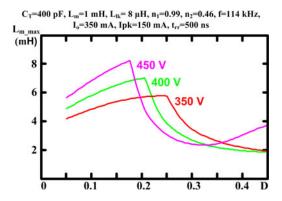

$V_g$ =400 V, C<sub>T</sub>=400 pF, L<sub>m</sub>=1 mH, L<sub>Ik</sub>= 8  $\mu$ H, n<sub>1</sub>=0.99, n<sub>2</sub>=0.46, f=114 kHz, I<sub>o</sub>=350 mA, STTH810G diodes, 06n60C3 MOSFETs

$V_{\rm g}$ =400 V,  $C_{\rm T}$ =400 pF,  $L_{\rm m}$ =1 mH,  $L_{\rm R}$ = 8 μH,  $n_{\rm I}$ =0.99,  $n_{\rm Z}$ =0.46, f=114 kHz,  $I_{\rm o}$ =350 mA, STTH810G diodes, 06n60C3 MOSFETs

Fig. 8. Voltage of  $C_{M2}$  for different duty cycles.

diodes affect this process and assuring that the aforementioned MOSFETs switch when the diodes have naturally turned ON and OFF

$$t_T = t_1 + t_2' + t_3''. (30)$$

Also, with (17), (24), and (28) and the time needed for each stage to finish  $(t_1, t_2', \text{ and } t_3'')$ , it is possible to predict the behavior of  $V_{CM\,2}$  during the transition time (i.e., dead time), as shown in Fig. 8. As the input voltage  $(V_q)$  is 400 V, ZVS is achieved when the voltage across  $C_{M2}$  reaches this value (solid black line). The end of each stage  $(t_1, t_2')$  and  $t_3''$  is represented with a dot of the corresponding color. As can be seen in Fig. 8(a), each stage shows a different behavior ruled by the previously defined equations. The first stage ends when the voltage is close to 120 V (which is the voltage across  $C_2$  when D = 0.30). The second one depends on the reverse recovery time  $t_{\rm rr}$  of  $D_2$ . The third stage lasts until the voltage across the parasitic capacitor  $C_{M2}$  is equal to the input voltage  $V_q$ . In that moment,  $V_{CM2}$  is clamped to  $V_q$  due to the parasitic diodes of the MOSFETs. In Fig. 8(a) and (b), the evolution of  $V_{CM2}$  during the third stage has been represented both with the clamping effect of the diodes and without it. In Fig. 8(b), the voltage of  $C_{M2}$  is represented for specific conditions and two possible duty cycles. As can be seen, for lower duty cycles, the relevant time is  $t_3''$ , while for higher ones it is  $t_2'$ .

Fig. 9. Minimum dead time needed for achieving ZVS.

It is important to highlight that  $t_T$  represents the minimum required time for the AHB to achieve ZVS. Hence, any dead time ( $t_{\text{dead}}$ ) longer than  $t_T$  will assure ZVS

$$t_{\rm dead} \ge t_T.$$

(31)

This condition will be taken into account in the design guidelines for a valid AHB (see Section V).

In Fig. 9, the minimum needed dead time  $t_T$  is represented for specific conditions as a function of D. As can be seen,  $t_1$ is quite short if compared with  $t_2'$  or  $t_3''$ . It should be taken into account that during the first stage, the current of the ideal transformer is added to the current of the magnetizing inductance. Hence, the amount of energy stored in the leakage inductance is high, and consequently, the parasitic capacitors are easily charged/discharged. As can be seen,  $t_2'$  increases with the duty cycle. It should be taken into account that for this representation, the value of  $t_{rr}$  and  $I_{pk}$  for different conditions of current and voltage (i.e., for different duty cycles) has been obtained by experimental analysis of the diodes. For low values of the duty cycle, the current demanded by the LED string is zero. Hence, the time of this second stage is nearly zero because diodes are nearly not biased. For higher values, the output current increases. As a consequence, the amount of energy stored in the leakage inductance decreases [see (23)] and slows down the charge/discharge process of the parasitic capacitors of the MOSFETs. Finally, the duration of the third stage  $(t_3'')$  decreases as the duty cycle increases. Although it should behave like  $t_2'$ (i.e., the higher the output current, the lower the leakage current), the starting voltage of this third stage increases with D so that the voltage swing of each capacitor is lower.

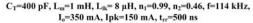

In Fig. 10, the minimum needed dead time for ZVS  $t_T$  is represented for different input voltages (solid lines). It should be highlighted that in this figure, the reverse peak current  $I_{\rm pk}$  and the reverse recovery time  $t_{\rm rr}$  of the diodes are considered constant and equal to the worst possible value for any input voltage and any duty cycle (in Figs. 8 and 9, the mathematical expressions of  $t_{\rm rr}$  and  $i_{\rm pk}$  for  $V_g=400\,{\rm V}$  were used). As can be seen, there are certain values of D for which the leakage inductance energy is so low (or  $V_g$  so high) that it is not possible to reach ZVS for the given conditions (for example,  $V_g=450\,{\rm V}$ ,  $L_m=1\,{\rm mH}$ , and  $D<0.1\,{\rm or}\,D>0.35$ ). This should be taken

Fig. 10.  $t_T$  for different input voltages  $(V_q)$ .

into account in the design process as ZVS should be reached preferably in nominal conditions.

Finally, the equations obtained during the previous sections not only allow us to predict the behavior of the voltage across the parasitic capacitors and the time needed for reaching ZVS, they also allow us to determine the maximum magnetizing inductance  $L_m$  that ensures ZVS. For doing so, the first step is calculating when the voltage of the parasitic capacitance  $V_{CM2}$  reaches its maximum during the third stage by differentiating (28) and making it equal to zero

$$0 = [V_g D - V_{CM2\_S2}(t'_2)] \omega \sin(\omega t''_{\text{max}}) + L_T \omega^2 I_{\text{lk\_S2}}(t'_2) \cos(\omega t''_{\text{max}})$$

(32)

where  $t''_{\text{max}}$  is the instant when the voltage of  $C_{M2}$  reaches a maximum due to the underdamped behavior of the equivalent circuit of stage three (see Fig. 7).

By using (28) and the value of  $t''_{\max}$  obtained from (32), it is possible to obtain the maximum value of the magnetizing inductance  $(L_{m_{\max}})$  for any duty cycle D and any input voltage  $V_g$ . For doing so, the condition to analyze is that when the magnetizing inductance is equal to  $L_{m_{\max}}$ , the voltage across the parasitic capacitance  $C_{M2}$  when it reaches its maximum  $(t''_{\max})$  is equal to the input voltage  $V_g$

$$V_{CM2\_S3}(t''_{\text{max}}) = V_g D - [V_g D - V_{CM2\_S2}(t'_2)] \cos(\omega t''_{\text{max}}) + (L_{m\_\text{max}} + L_{\text{lk}})\omega I_{\text{lk\_S2}}(t'_2) \sin(\omega t''_{\text{max}}) = V_g.$$

(33)

It should be taken into account that  $V_{CM\,2\_s2}(t_2')$  and  $I_{lk\_s2}(t_2')$  are obtained from equations that also depend on the magnetizing inductance. Hence, there is no analytical solution and a calculation software, such as MathCad, needs to be used. In Fig. 11, the value of  $L_{m\_max}$  is given for specific conditions as an example. As can be seen, the maximum value of the magnetizing inductance varies as D is modified. Assuring ZVS for the whole range involves analyzing the worst situation and selecting a magnetizing inductance lower than the corresponding value of  $L_{m\_max}$ . In Fig. 11, the worst situation takes place when D=0.45, and consequently,  $L_m$  should be lower than 2 mH in order to ensure ZVS in any situation.

Fig. 11.  $L_{m \perp m ax}$  for different values of  $V_g$  and D.

### V. DESIGN GUIDELINE

The design of this AHB for street lighting needs to consider the equations defined in the previous two sections in order to obtain a high-efficiency converter. The design of this two-stage topology should begin with the second stages (i.e., the AHB) but fixing the value of the first-stage output voltage and its ripple, which cannot be neglected due to the absence of electrolytic capacitors. Typical values, taking into account that no electrolytic capacitors are going to be used, are around 10%. The other values that should be known are given by the LED strings: number of LEDs per string (N), knee voltage of each LED ( $V_{\gamma}$ \_LED), its dynamic resistance (R\_LED), and its nominal current (I\_nom) or its nominal power (P\_nom).

The maximum and minimum values of the output voltages of the AHB for total dimming can be calculated as

$$V_{\text{out\_max}} = NV_{\gamma \text{\_LED}} + NR_{\text{LED}}I_{\text{nom}} = \frac{P_{\text{nom}\cdot N}}{I_{\text{nom}}}$$

(34)

$$V_{\text{out\_min}} = NV_{\gamma \text{\_LED}}.$$

(35)

To achieve ZVS, a suitable value for the total dead time (considering both transitions) may be around 15%–20%. This leads to a maximum duty cycle ( $D_{\rm max}$ ) of 43%–40%. Using (1), (4), and (34)

$$n_1 + n_2 = \frac{N(P_{\text{nom}}/I_{\text{nom}})}{V_{g\_{\text{nom}}} (1 - (r_v/2))} \times \frac{1}{D_{\text{max}} (1 - D_{\text{max}})}.$$

(36)

The value of  $D_{\min}$  can be obtained from (4) and (36), considering the minimum output voltage (35) and the maximum input voltage (1). Once  $D_{\min}$  and  $D_{\max}$  are known, it is possible to obtain  $D_{\text{Im}0}$  from (12), and finally,  $n_1$  and  $n_2$  from (11) and (36).

With these parameters, it is possible to design the output inductor and the transformer by standard methods. Once they are designed, and taking into account the resulting leakage inductance of the transformer, it is possible to use the equations in Section IV for fixing the necessary magnetizing inductance of the transformer. With (33), it is possible to determine the value of  $L_{m\_max}$ . As has been said, this equation cannot be solved analytically. The chosen magnetizing inductance needs to assure ZVS for any condition (input voltage  $V_g$  and duty cycle D) and it can easily be obtained by wisely choosing the gap

Fig. 12. Photograph of the prototype.

in the core. Nevertheless, this equation does not provide any kind of information about the time needed for reaching ZVS. With the selected value of  $L_m$ , it is possible to use (30) in order to obtain the value of the minimum dead time  $t_T$  required for reaching ZVS. If this time represents an excessive percentage of the total switching period, the maximum duty cycle may be compromised and it is necessary to reduce  $t_T$ . For doing so, the value of  $L_m$  needs to be reduced. That increases the amount of energy stored in the resonant circuit during the third stage of the transition and it also increases its resonant frequency. As a consequence, the parasitic capacitances are charged/discharged quicker and  $t_T$  is shorter (i.e., ZVS is reached earlier).

### VI. EXPERIMENTAL RESULTS

A prototype of the AHB (second stage) has been built and tested (see Fig. 12). It is designed for supplying a 40-W LED string with  $NV_{\gamma\_\rm LED}=95~\rm V$  and  $NR_{\rm LED}=140~\Omega$ . The nominal input voltage is (400  $\pm$  7%) V. The MOSFETs are 06N60C3 and they have a parasitic capacitance of 200 pF each at  $V_{\rm DS}=25~\rm V$ . The transformer is built in an E30 core and the output inductor in an E20 one. The rectifier diodes are STTH810G.  $C_{\rm pos}$  and  $C_{\rm neg}$  are 300 nF capacitors (three 100 nF capacitors in parallel each) and  $C_f$  is a 1- $\mu\rm F$  metallized plastic polypropylene capacitor. The switching frequency is 114 kHz in order to obtain a switching period considerably longer than the dead times.

By using the equations in Sections III and V and fixing the maximum duty cycle (in this case,  $D_{\rm max}=0.4$ ), it is possible to obtain  $D_{\rm Im0}$ ,  $D_{\rm min}$ ,  $n_1$ , and  $n_2$  (equal to 0.327, 0.253, 1.075, and 0.521, respectively, in the built prototype). With these values, the design of the output inductor and the transformer and the selection of the semiconductors can be carried out by achieving the minimization of the average value of the magnetizing current. The optimum design for this prototype leads to an 8- $\mu$ H transformer leakage inductance and a 2.5-mH filter inductor. Once this point of the design process is completed, it is possible to use (33) in order to determine the maximum value of  $L_m$  (see  $L_{m\_max}$  in Fig. 11). In this case, a magnetizing inductance of 2 mH assures ZVS for any condition. Nevertheless, the resulting  $t_T$  for this value (around 4  $\mu$ s for each transition) is

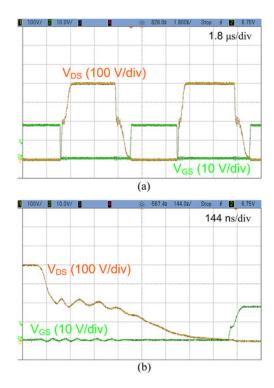

Fig. 13. (a)  $V_{\rm GS}$  and  $V_{\rm DS}$  of  $M_2$ . (b) Detail of both voltages during the dead time.

excessively long for the 114-kHz switching frequency. Hence, the transformer gap is increased so that the resulting magnetizing inductance of the transformer is reduced to 1 mH and  $t_T$  for the worst possible situation is reduced to 1  $\mu$ s (i.e., each transition lasts 10% of the total period).

In Fig. 13(a), the  $V_{\rm DS}$  and the  $V_{\rm GS}$  of MOSFET  $M_2$  are shown when the prototype is providing the nominal current. As can be seen, ZVS is achieved. This means that the amount of energy stored in the leakage inductance is enough. In Fig. 13(b), a detail of the transition is shown.

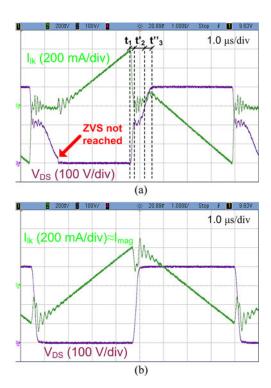

In Fig. 14(a) and (b), the voltage  $V_{\rm DS}$  across one of the MOSFETs and the leakage inductance current are shown at full load and no-load conditions. In both situations, ZVS is achieved. As can be seen in Fig. 14(a), at the beginning of  $t_2'$  (i.e., second stage of the dead time), the leakage current is strongly reduced as a consequence of the reverse recovery current of the diode that is being turned OFF and the current of the diode that is being turned ON (which is driving a current equal to the output current plus the other diode current). Nevertheless, the remaining amount of energy stored in the leakage inductance is high enough in order to finally reach ZVS. As can be seen in the highlighted area in Fig. 14(a), ZVS is not fully reached when turning ON the other MOSFET. Its corresponding dead time was slightly reduced so that the effect of non-ZVS could be seen. In Fig. 14(b), the ZVS at no-load is shown. Considering that the energy stored in the leakage inductance not only depends on the load current, but also on the magnetizing current, it is possible to achieve ZVS even at no load. The reduction in the leakage inductance current in the second stage of the dead time is considerably lower because the reflected current in the pri-

Fig. 14. Magnetizing current and  $V_{\rm DS}$  (a) at full load and (b) at no-load conditions.

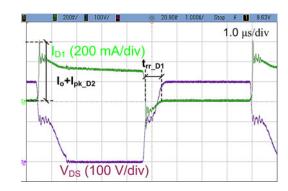

Fig. 15.  $D_1$  current and  $V_{DS}$  of  $M_2$ .

mary winding of the transformer is lower (i.e., the load current is zero and the reverse recovery current is quite low). Hence, with this design, it is possible to reach ZVS at any load.

In Fig. 15, the current through diode  $D_1$  is shown. As can be seen, when the diode is turned OFF, its current is equal to the reverse recovery current with a considerably long  $t_{\rm rr}$ . When it is turned ON, its current is equal to the output current plus the reverse recovery current of the other diode  $(D_2)$ . This leads to the aforementioned reduction in the leakage inductance current during  $t_2'$  and  $t_3''$  (see Fig. 14).

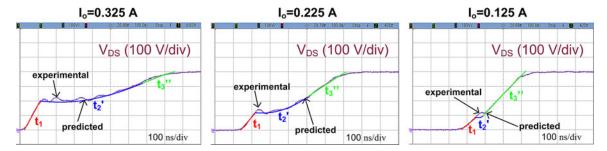

A comparison between the model of the dead time and the experimental results is shown in Fig. 16 for different duty cycles at nominal input voltage. The only different between the model and the experimental results is that the former does not include the resonance at the beginning of the second stage of the transitory caused by the forced variation of the leakage inductance current due to the reversed bias of the diode that was turned ON.

Fig. 16. Comparison of experimental results and the proposed model. Red line- $t_1$  (first stage of the dead time), blue line- $t_2$  (second stage of the dead time), and green line- $t_3$  (third stage of the dead time).

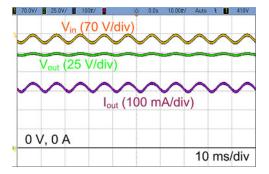

Fig. 17. Input voltage, output voltage, and output current.

In Fig. 17, the input voltage, output voltage, and output current of the AHB are shown when the input voltage (output voltage of the first stage) is affected by a 100-Hz ripple. It should be taken into account that because the load is an LED string, the relative ripple of the output current is always considerably higher than the relative ripple of the output voltage. In this case, the control of the AHB is not optimized and it has been designed in order to have a 10% peak-to-peak current ripple, which means a 1.6% peak-to-peak ripple in the output voltage. Without the control (i.e., in open loop), the relative peak-to-peak ripple in the input voltage would be completely transferred to the output voltage and the current peak-to-peak ripple would be as high as 50%.

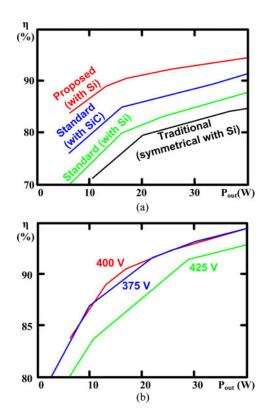

Finally, in Fig. 18(a), the efficiency at different loads for different design considerations is shown. The "traditional design" implies that the secondary windings of the transformer are symmetrical and that silicon diodes are used. As stated earlier, this implies that ZVS is not easy to obtain in both MOSFETs due to the nonzero average value of the magnetizing current of the transformer. In this design, the dead times have been independently optimized in order to be as close as possible to ZVS although it was not possible to reach it in certain conditions. The "standard design" implies that the average magnetizing current is minimized as explained in this paper, but the transient during the dead time is not analyzed in order to determine the optimum value of the magnetizing inductance. On the other hand, in the "proposed design" both considerations are made (average magnetizing current reduction and calculation of the optimum magnetizing inductance). In this way, the "proposed" and the "standard" designs can be directly compared since the only hardware difference between them is the gap of the transformer (i.e., the turns ratios are the same in both cases). Two

Fig. 18. Efficiency of the prototype for (a) different design methods and (b) different input voltages (using the design proposed in this paper).

"standard designs" are proposed: one with Si ultrafast diodes (the same used in the "proposed design") and the other with SiC Schottky diodes. As can be seen, the "standard design" with Si diodes has the worst efficiency. Using SiC Schottky diodes improves the efficiency by 2% as the switching losses in secondary switches are the most critical point in this topology. Nevertheless, the "proposed design" using the same Si diodes as those used in the "standard design" presents the best efficiency results. This means that the AHB can be implemented using low-cost components (i.e., Si technology) but maintaining high efficiency if the design rules proposed in this paper are considered. If the "standard" and the "proposed" designs are compared to the "traditional" one, it should be taken into account that the main difference is the transformer secondary windings (the size of the core is the same in all the designs for proper comparison). As can be seen, the efficiency obtained with the "traditional design" is lower. Conduction losses in the transformer were higher and switching losses in the MOSFETs were also increased, as it was harder to reach ZVS.

In Fig. 18(b), the efficiency achieved with the design proposed in this paper and for different input voltages is shown. As can be seen, at nominal load, the efficiency is as high as 94.5%. Considering that the first stage may reach an efficiency as high as 97%, the overall efficiency of the whole topology is around 91.5%. This high efficiency leads to reduced temperature in components, which allows the prototype to be built without a heat sink. The efficiency at 425 V is lower than the efficiency at 375 or 400 V. At this input voltage, ZVS is partially lost ( $L_{m\_mag}$  and  $t_T$  were calculated for a 400-V input voltage), and consequently, this increases the switching losses in the diodes and the MOSFETs.

### VII. CONCLUSION

The use of HB-LEDs has led to the development of new topologies for LED-based lighting. Hence, high-efficiency high-reliability converters have been proposed in the recent years and dimming techniques have also been developed.

In this paper, a two-stage solution for LED-based street lighting applications is proposed. The first stage is the well-known boost converter. This paper is focused on the second stage, the AHB. Modifying the traditional design typically used for this converter, it is possible to optimize it for the LED string. As a result, its efficiency and reliability are boosted. This new design has two advantages. First, the average value of the magnetizing current is reduced by the asymmetrical design of its transformer, what implies a reduction in conduction losses. Second, a model for describing transitions is developed. It can be used in the design process for reducing switching losses in MOSFETs and diodes.

An efficiency of 94.5% has been obtained for a 40-W prototype. Experimental results also indicate that the proposed model is accurate and helpful for designing AHB optimized for LEDbased applications.

### REFERENCES

- T. Siew-Chong, "Level driving approach for improving electrical-tooptical energy-conversion efficiency of fast-response saturable lighting devices," *IEEE Trans. Ind. Electron.*, vol. 57, no. 4, pp. 1342–1353, Apr. 2010.

- [2] W. Beibei, R. Xinbo, Y. Kai, and X. Ming, "A method of reducing the peak-to-average ratio of LED current for electrolytic capacitor-less AC-DC drivers," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 592–601, Mar. 2010.

- [3] L. Xingming and Z. Jing, "An intelligent driver for light emitting diode street lighting," in *Proc. World Automation Congr. (WAC)*, 2008, pp. 1–5.

- [4] D. G. Lamar, J. Sebastián, A. Rodríguez, M. Rodríguez, and M. M. Hernando, "A very simple control strategy for power factor correctors driving high-brightness LEDs," *IEEE Trans. Power Electron.*, vol. 24, no. 8, pp. 2032–2042, Aug. 2009.

- [5] D. G. Lamar, J. Sebastian, M. Arias, and M. M. Hernando, "A low-cost AC-DC high-brightness LED driver with power factor correction based on standard peak-current mode integrated controllers," in *Proc. IEEE Energy Convers. Congr. Expo. (ECCE)*, 2010, pp. 463–470.

- [6] X. Qu, S. C. Wong, and C. K. Tse, "Resonance-assisted buck converter for offline driving of power LED replacement lamps," *IEEE Trans. Power Electron.*, vol. 26, no. 2, pp. 532–540, Feb. 2011.

- [7] Q. Hu and R. Zane, "Minimizing required energy storage in off-line LED drivers based on series-input converter modules," *IEEE Trans. Power Electron.*, vol. 26, no. 10, pp. 2887–2895, Oct. 2011.

- [8] H. Qingcong and R. Zane, "LED driver circuit with series-input-connected converter cells operating in continuous conduction mode," *IEEE Trans. Power Electron.*, vol. 25, no. 3, pp. 574–582, Mar. 2010.

- [9] L. Wai-Keung, K. H. Loo, T. Siew-Chong, Y. M. Lai, and C. K. Tse, "Bilevel current driving technique for LEDs," *IEEE Trans. Power Electron.*, vol. 24, no. 12, pp. 2920–2932, Dec. 2009.

- [10] B. R. Lin and C. L. Huang, "Analysis and implementation of an integrated sepic-forward converter for photovoltaic-based light emitting diode lighting," *Power Electron.*, *IET*, vol. 2, no. 6, pp. 635–645, Nov. 2009.

- [11] D. Gacio, J. M. Alonso, A. J. Calleja, J. Garcia, and M. Rico-Secades, "A universal-input single-stage high-power-factor power supply for HB-LEDs based on integrated buck-flyback converter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 2, pp. 589–599, Feb. 2011.

- [12] H. Yuequan and M. M. Jovanovic, "LED driver with self-adaptive drive voltage," *IEEE Trans. Power Electron.*, vol. 23, no. 6, pp. 3116–3125, Nov. 2008.

- [13] ST, "AN3105 Application note: 48 V-130 W high efficiency converter with PFC for LED street lighting applications - European version," ST online database.

- [14] Q. Xiaohui, W. Siu-Chung, and C. K. Tse, "Noncascading structure for electronic ballast design for multiple LED lamps with independent brightness control," *IEEE Trans. Power Electron.*, vol. 25, no. 2, pp. 331–340, Feb. 2010.

- [15] W. Jian-Min, W. Sen-Tung, J. Yanfeng, and C. Huang-Jen, "A dual-mode controller for the boost PFC converter," *IEEE Trans. Ind. Electron.*, vol. 58, no. 1, p. 369-372, Jan. 2011.

- [16] T. Jiun-Ren, W. Tsai-Fu, W. Chang-Yu, C. Yaow-Ming, and L. Ming-Chuan, "Interleaving phase shifters for critical-mode boost PFC," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp. 1348–1357, May 2008.

- [17] Y. Hu, L. Huber, and M. Jovanovic, "Single-stage, universal-input AC/DC LED driver with current-controlled variable PFC boost inductor," *IEEE Trans. Power Electron.*, vol. PP, no. 99, p. 1, Oct. 2010.

- [18] M. M. Hernando, A. Fernandez, J. Garcia, D. G. Lamar, and M. Rascon, "Comparing Si and SiC diode performance in commercial AC-to-DC rectifiers with power-factor correction," *IEEE Trans. Ind. Electron.*, vol. 53, no. 2, pp. 705–707, Apr. 2006.

- [19] X. Xiaojun, L. Wei, and A. Q. Huang, "Two-phase interleaved critical mode PFC boost converter with closed loop interleaving strategy," *IEEE Trans. Power Electron.*, vol. 24, no. 12, pp. 3003–3013, Dec. 2009.

- [20] J. Sebastian, J. A. Cobos, O. Garcia, and J. Uceda, "An overall study of the half-bridge complementary-control DC-to-DC converter," in *Proc. 26th Annu. IEEE Power Electron. Spec. Conf. (PESC)*, 1995, pp. 1229–1235.

- [21] R. Oruganti, H. P. Chee, J. T. K. Guan, and C. L. Ah, "Soft-switched DC/DC converter with PWM control," *IEEE Trans. Power Electron.*, vol. 13, no. 1, pp. 102–114, Jan. 1998.

- [22] R. Miftakhutdinov, A. Nemchinov, V. Meleshin, and S. Fraidlin, "Modified asymmetrical ZVS half-bridge DC-DC converter," in *Proc. 14th Annu. Appl. Power Electron. Conf. Expo. (APEC)*, 1999, pp. 567–574.

- [23] O. Garcia, J. A. Cobos, J. Uceda, and J. Sebastian, "Zero voltage switching in the PWM half bridge topology with complementary control and synchronous rectification," in *Proc. 26th Ann. IEEE Power Electron. Spec. Conf. (PESC)*, 1995, pp. 286–291.

- [24] W. Eberle, H. Yongtao, L. Yan-Fei, and Y. Sheng, "An overall study of the asymmetrical half-bridge with unbalanced transformer turns under current mode control," in *Proc. 19th Annu. IEEE Appl. Power Electron. Conf. Expo.* (APEC), 2004, pp. 1083–1089.

- [25] C. L. Ma and P. O. Lauritzen, "A simple power diode model with forward and reverse recovery," *IEEE Trans. Power Electron.*, vol. 8, no. 4, pp. 342– 346, Oct. 1993.

- [26] H. Wu, R. Dougal, and C. Jin, "Modeling power diode by combining the behavioral and the physical model," in *Proc. 31st IEEE Annu. Conf. Ind. Electron. Soc. (IECON)*, 2005, p. 6.

**Manuel Arias** (S'05–M'10) was born in Oviedo, Spain, in 1980. He received the M.Sc. degree in electrical engineering and the Ph.D. degree, from the University of Oviedo, Spain, in 2005 and 2010, respectively.

Since February 2005, he has been a Researcher in the Department of Electrical and Electronic Engineering, and since February 2007 he has also been an Assistant Professor of electronics, at the University of Oviedo. His research interests include ac-dc and dc-dc converters, UPSs and LED-based lighting.

**Diego G. Lamar** (S'05–M'09) was born in Zaragoza, Spain, in 1974. He received the M.Sc. and Ph.D. degrees in electrical engineering from the Universidad de Oviedo, Spain, in 2003 and 2008, respectively.

In 2003, he became a Research Engineer at the University of Oviedo and since September 2005, he has also been an Assistant Professor. His research interests are switching-mode power supplies, converter modelling, and power-factor-correction converters.

Francisco M. Fernández Linera (M'96) was born in Cangas de Narcea, Spain, in 1966. He received the M.Sc. and Ph.D. degrees in electrical engineering from the University of Oviedo, Gijón, Spain, in 1990 and 1997, respectively.

He is currently an Associate Professor at the University of Oviedo, where he is involved in several research projects. His main research interests are industrial control, switching-mode power supplies and converter modeling.

**Didier Balocco** received the Engineer diploma from the "Ecole Nationale Supérieure d'Electronique et de RadioElectricité de Bordeaux," France, in 1992 and the Ph.D. degree in electrical engineering from the University of Bordeaux, in 1997.

In 1996, he joined Alcatel Converters (now AEG Power Solutions) as a Research Engineer. Since 2000, he has managed the research activities at AEG Power Solutions. He has published more than ten papers on power electronics. He holds four patents, three of which are pending. His main research interests are

switching mode power supply, converter stability, high power factor rectifiers for telecom and industrial application. He has developed several projects for telecom domain and lighting.

Almadidi Aguissa Diallo received the Engineer diploma in the "Ecole Nationale d.Ingénieur de Bamako," Mali, in 1977, the Specialisation diploma of the "Ecole Supérieure d'Electricité (ESE) de Gif/Yvette," France, in 1979, and the Ph.D. degree in electronic engineering in 1984 from the University of Paris-Sud Orsay where he also served as an Assistant for several years.

In 1984, he joined AEA (Atelier d'Electronique et d'Automatisme), a company that later became Alcatel Converters and then AEG power Solutions, as a

Development Engineer, and then became a Research Engineer. Since 2003, he has managed operational marketing as Product Line Manager at AEG Power Solutions. He has published some papers on power electronics. He holds four patents, one of which is pending. His main interests are switching mode power supply, converter reliability, high efficiency and high power factor rectifiers for telecom and industrial application, smart grid solutions. He developed and introduced several projects for telecom domain, smart lighting, battery chargers and smart grid.

**Javier Sebastián** (M'87–SM'11) was born in Madrid, Spain, in 1958. He received the M.Sc. degree from the Polytechnic University of Madrid, Madrid, in 1981 and the Ph.D. degree from the Universidad de Oviedo, Gijón, Spain, in 1985.

He was an Assistant Professor and an Associate Professor at both the Polytechnic University of Madrid and the Universidad de Oviedo. Since 1992, he has been with the Universidad de Oviedo, where he is currently a Professor. His research interests are switching-mode power supplies, modeling of dc-to-

dc converters, low-output-voltage dc-to-dc converters, and high-power-factor rectifiers.