# **NUC970 Family Programming Guide**

#### **Document Information**

| Abstract | This document introduces the control sequence of NUC970 family peripherals. |

|----------|-----------------------------------------------------------------------------|

| Apply to | NUC970 family, including NUC972, NUC973, NUC976 and NUC977.                 |

The information described in this document is the exclusive intellectual property of Nuvoton Technology Corporation and shall not be reproduced without permission from Nuvoton.

Nuvoton is providing this document only for reference purposes of NuMicro microcontroller based system design.

Nuvoton assumes no responsibility for errors or omissions.

All data and specifications are subject to change without notice.

For additional information or questions, please contact: Nuvoton Technology Corporation.

www.nuvoton.com

### **Table of Contents**

| 1 | SYSTEM MANAGER                       | 12  |

|---|--------------------------------------|-----|

|   | 1.1 Overview                         | 12  |

|   | 1.2 Register Map                     | 12  |

|   | 1.3 Functional Description           |     |

|   | 1.3.1Multiple Function Control       |     |

|   | 1.3.2Low Voltage Detect / Reset      |     |

|   | 1.3.3USB ID Detection                | 14  |

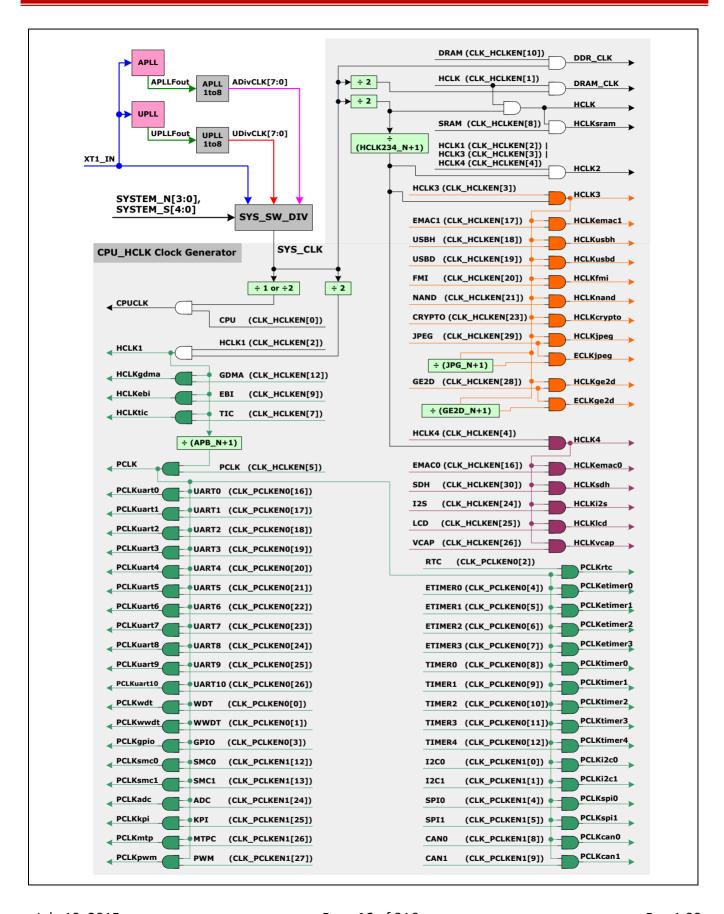

| 2 | CLOCK CONTROLLER                     | 15  |

| _ | 2.1 Overview                         |     |

|   | 2.2 Features                         |     |

|   | 2.3 Block Diagram                    |     |

|   | 2.4 Register Map                     |     |

|   | 2.5 Functional Description           |     |

|   | 2.5.1Module Clock On/Off             |     |

|   | 2.5.2Clock Divider                   |     |

|   | 2.5.3PLL Setting                     | 18  |

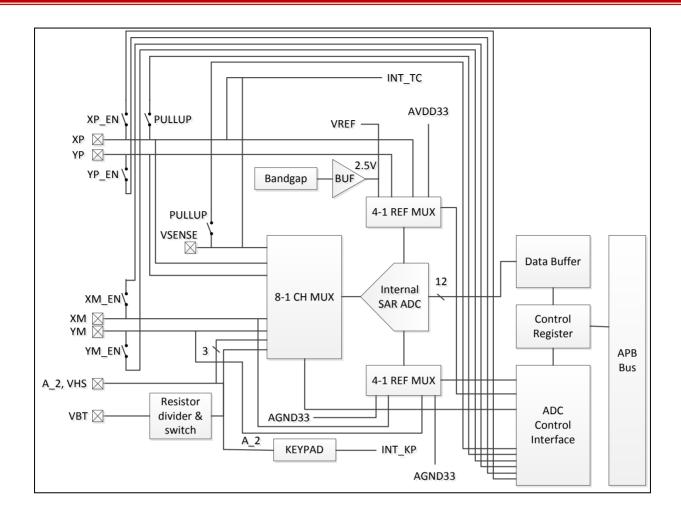

| 3 | ANALOG TO DIGITAL CONVEDTED (ADC)    | 2.0 |

| 3 | ANALOG TO DIGITAL CONVERTER (ADC)    |     |

|   | 3.1 Overview                         |     |

|   | 3.2 Features                         |     |

|   | 3.3 Block Diagram                    |     |

|   | 3.4 Register Map                     | 21  |

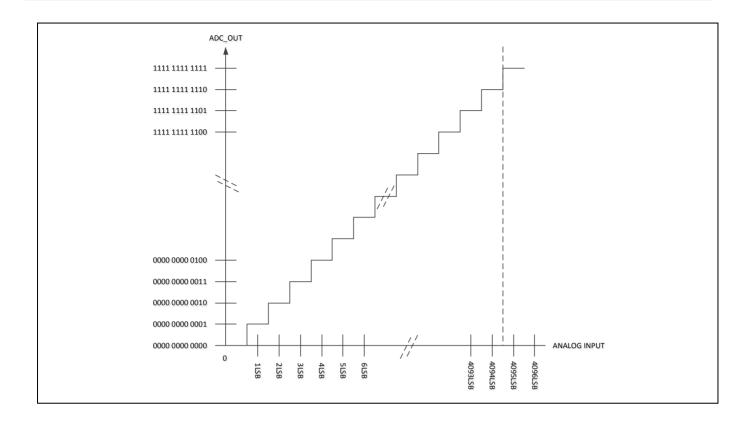

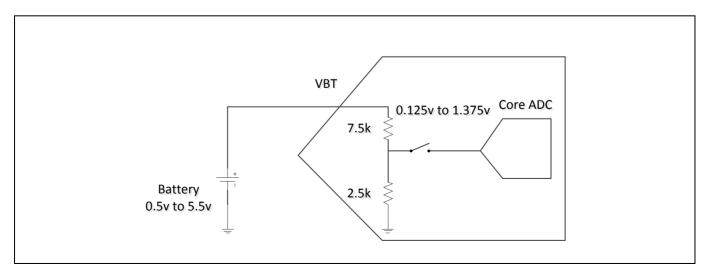

|   | 3.5 Functional Description           | 22  |

|   | 3.5.1Basic Configuration             |     |

|   | 3.5.2ADC Transfer Function           |     |

|   | 3.5.3Normal Detection                |     |

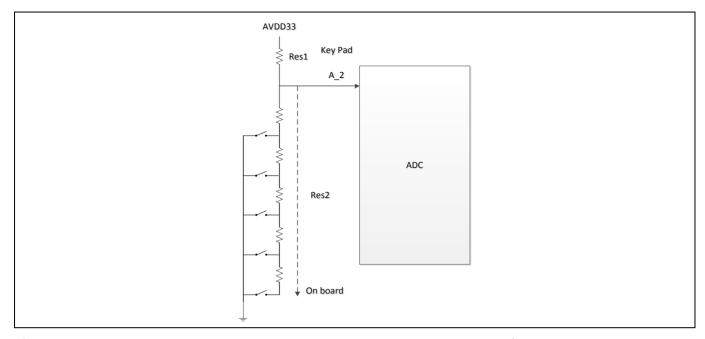

|   | 3.5.5Key Pad Scan                    |     |

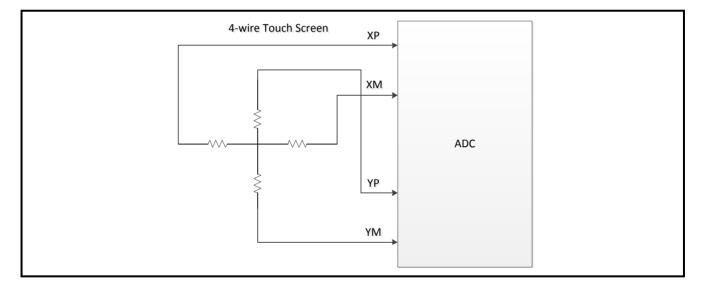

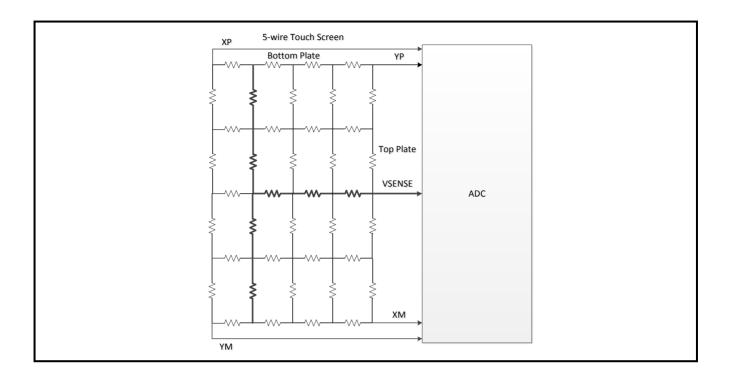

|   | 3.5.64-wire and 5-wire Touch Screen  |     |

|   | 3.5.74-wire Pressure Measurement     | 29  |

|   | ADVANCED INTERRUPT CONTROL LED (ALC) | 0.4 |

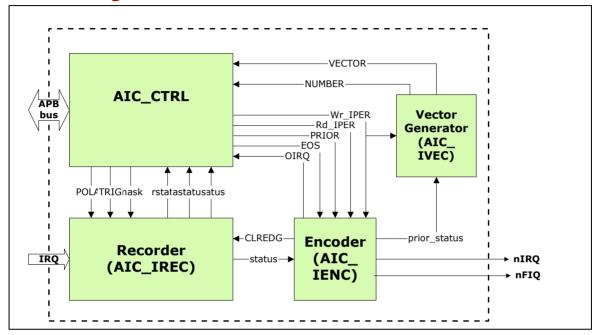

| 4 | ADVANCED INTERRUPT CONTROLLER (AIC)  |     |

|   | 4.1 Overview                         | 31  |

|   | 4.2 Features                         | 31 |

|---|--------------------------------------|----|

|   | 4.3 Block Diagram                    | 32 |

|   | 4.4 Register Map                     | 32 |

|   | 4.5 Functional Description           |    |

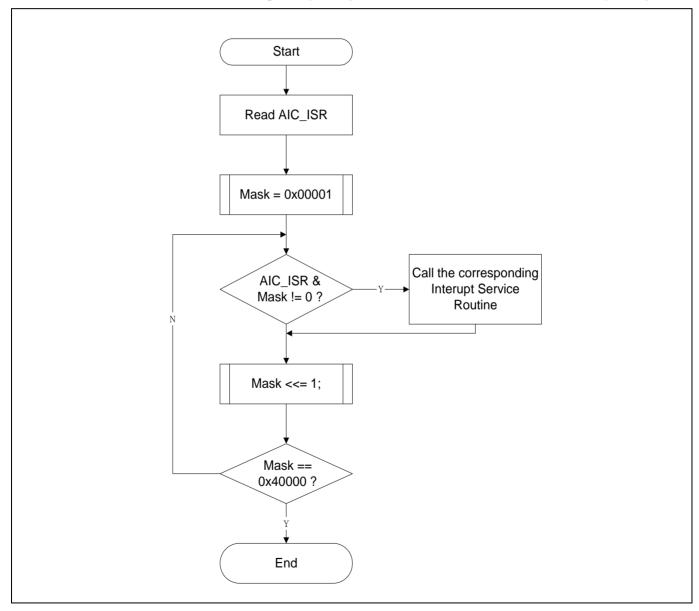

|   | 4.5.1Interrupt channel configuration |    |

|   | 4.5.2Interrupt Masking               |    |

|   | 4.5.3Interrupt Clearing and Setting  |    |

|   | 4.5.4Software Priority Scheme        |    |

|   | 4.5.5Hardware Priority Scheme        |    |

|   | 4.5.6Interrupt Sources               |    |

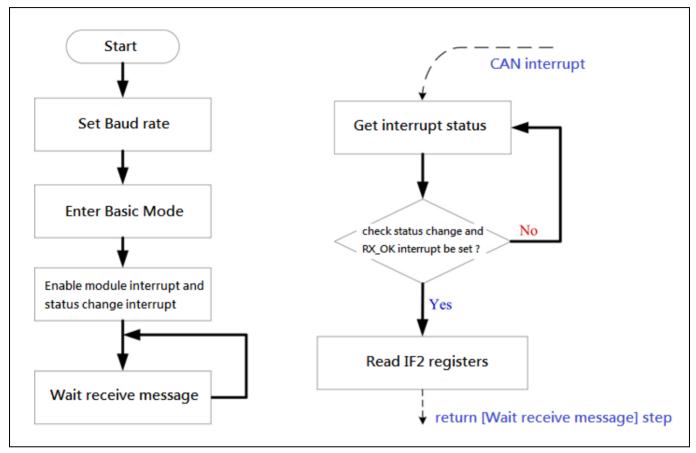

| _ | 5 CAN                                | 40 |

| 3 |                                      |    |

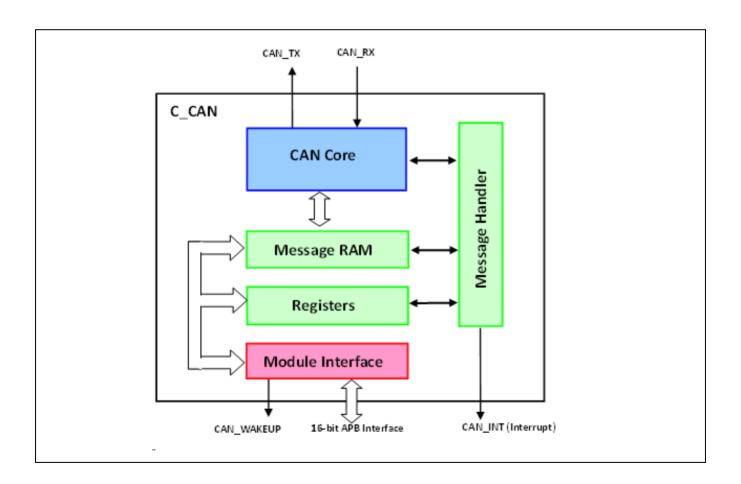

|   | 5.1 Overview                         |    |

|   | 5.2 Features                         |    |

|   | 5.3 Block Diagram                    | 40 |

|   | 5.4 Register Map                     | 41 |

|   | 5.5 Functional Description           | 43 |

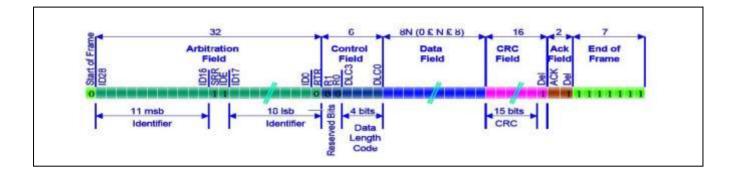

|   | 5.5.1CAN Protocol                    |    |

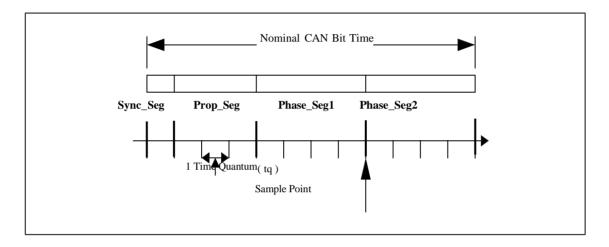

|   | 5.5.2CAN Baud Rate Setting           |    |

|   | 5.5.3CAN Module Register             |    |

|   | 5.5.4Transfer CAN Message            |    |

|   | 5.5.5Receive CAN Message             |    |

|   | 3.3.0 Wakeup Fullction               |    |

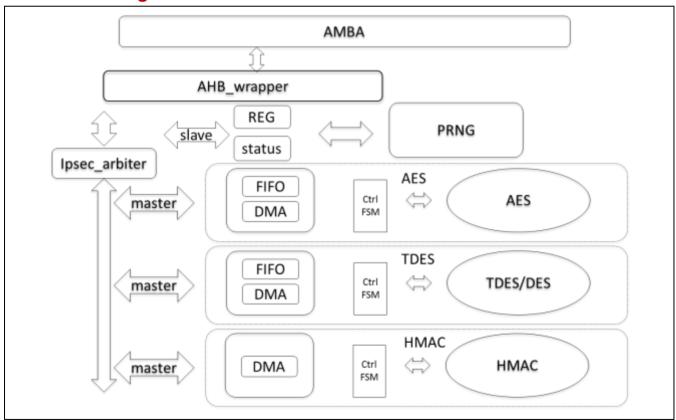

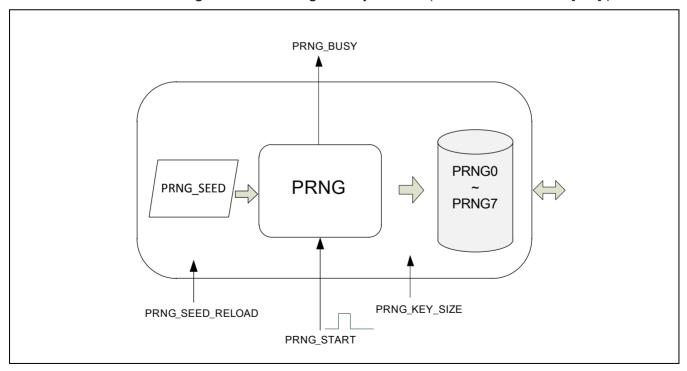

| 6 | 6 CRYPTOGRAPHIC ACCELERATOR          | 51 |

|   | 6.1 Overview                         | 51 |

|   | 6.2 Features                         | 51 |

|   | 6.3 Block Diagram                    | 52 |

|   | 6.4 Register Map                     | 52 |

|   | 6.5 Functional Description           | 57 |

|   | 6.5.1Data Access                     | 58 |

|   | 6.5.2Channel Expansion               |    |

|   | 6.5.3PRNG                            |    |

|   | 6.5.4AES                             |    |

|   | 6.5.5DES/TDES                        |    |

|   | 6.5.6SHA                             | 63 |

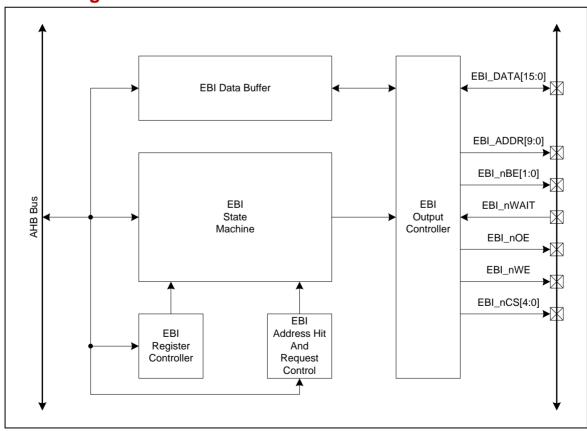

| 7 | 7 EXTERNAL BUS INTERFACE (EBI)       | 66 |

|   | 7.1 Overview                         |    |

|   | 7.2 Features                         |    |

|   | 7.3 Block Diagram                    |    |

|   | <u> </u>                             |    |

|    | 7.4 Register Map                     | 67  |

|----|--------------------------------------|-----|

|    | 7.5 Functional Description           | 67  |

|    | 7.5.1Basic Configuration             | 67  |

|    | 7.5.2Memory Space and Control        | 67  |

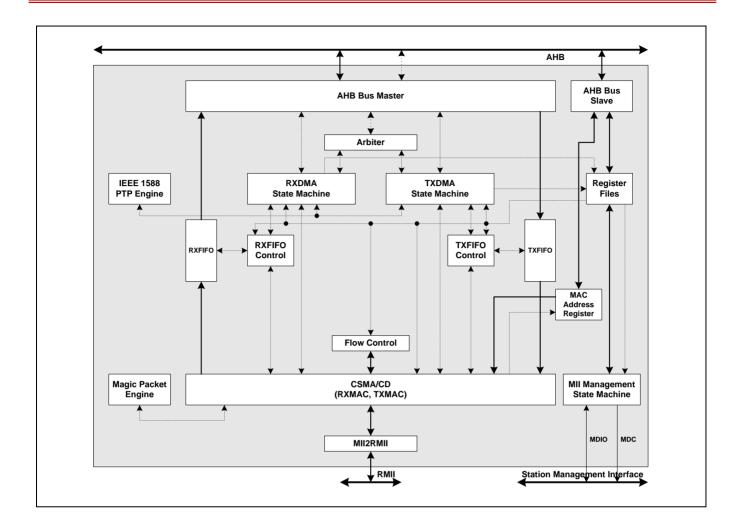

| 8  | ETHERNET MAC CONTROLLER (EMAC)       | 69  |

|    | 8.1 Overview                         | 69  |

|    | 8.2 Features                         | 69  |

|    | 8.3 Block Diagram                    | 69  |

|    | 8.4 Register Map                     | 70  |

|    | 8.5 Functional Description           | 72  |

|    | 8.5.1PHY Control                     | 72  |

|    | 8.5.2CAM Configuration               |     |

|    | 8.5.3Control Frame                   |     |

|    | 8.5.4Wake on Lan (WoL)               |     |

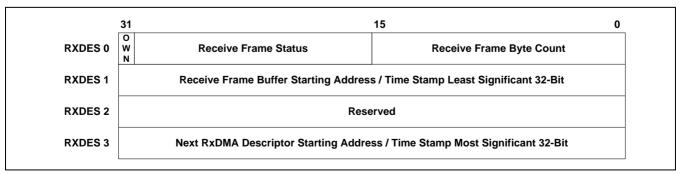

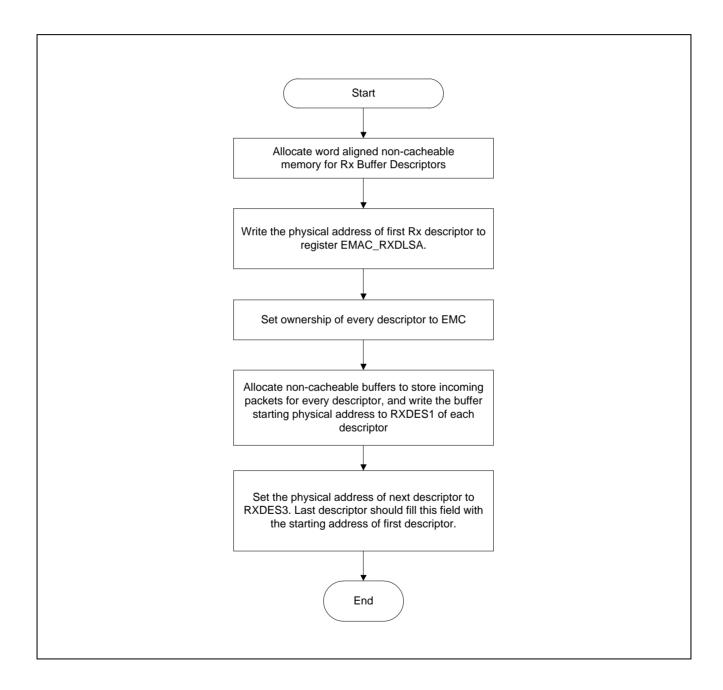

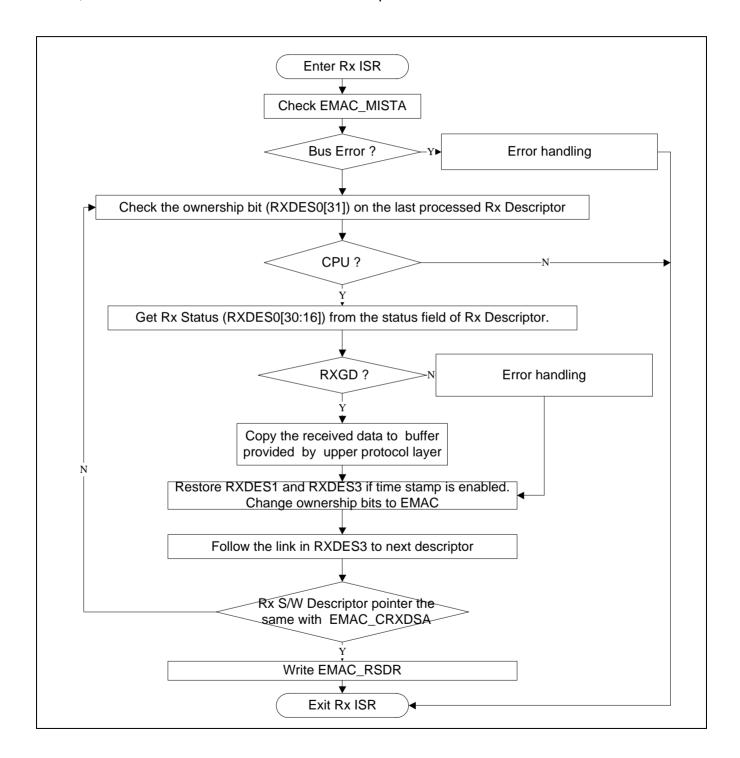

|    | 8.5.5Packet Receive                  |     |

|    | 8.5.6Packet Transmit                 |     |

|    | 8.5.8Error Handling                  |     |

|    |                                      |     |

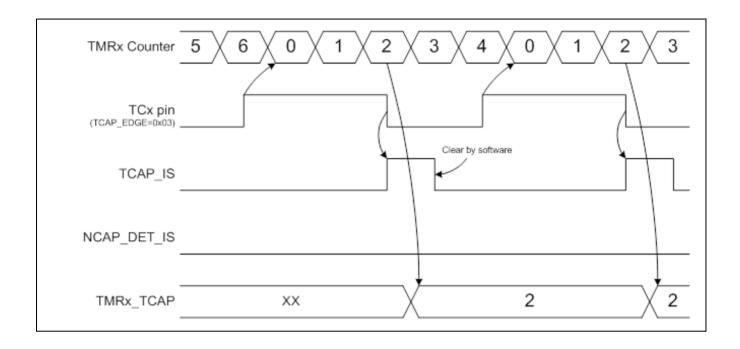

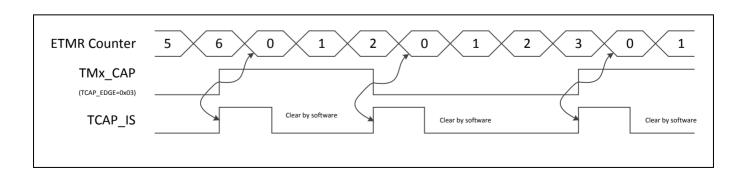

| 9  | ENHANCED TIMER CONTROLLER (ETMR)     | 91  |

|    | 9.1 Overview                         | 91  |

|    | 9.2 Features                         | 91  |

|    | 9.3 Block Diagram                    | 91  |

|    | 9.4 Register Map                     | 91  |

|    | 9.5 Functional Description           | 92  |

|    | 9.5.1Timer Initialization            |     |

|    | 9.5.2Timer Capture Initialization    |     |

|    | 9.5.3Interrupt Handling              |     |

|    | 9.5.4Timer Frequency                 |     |

|    | 9.5.5One-Shot Mode9.5.6Periodic Mode |     |

|    | 9.5.7Toggle Mode                     |     |

|    | 9.5.8Continuous Mode                 |     |

|    | 9.5.9Free Counting Mode              |     |

|    | 9.5.10 Trigger Counting Mode         |     |

|    | 9.5.11 Counter Reset Mode            |     |

|    | 9.5.12 Capture Debounce              | 99  |

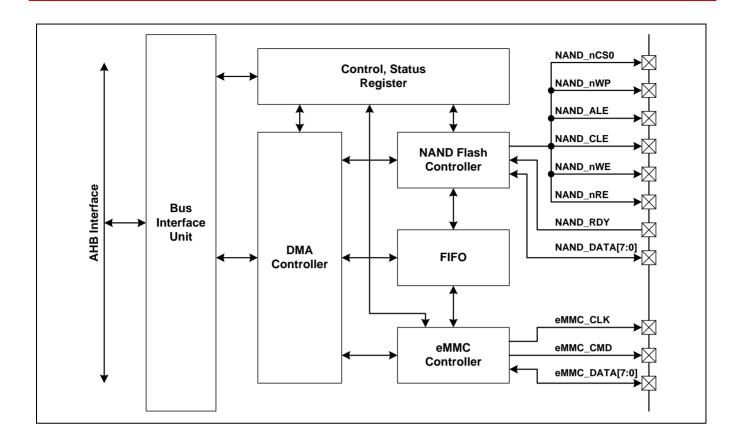

| 10 | FLASH MEMORY INTERFACE               | 100 |

|    | 10.1 Overview                        |     |

|    | 10.2 Features                        | 100 |

|    |                                      |     |

| 10.3 Bloc | k Diagram                              | 100 |

|-----------|----------------------------------------|-----|

| 10.4 Regi | ister Map                              | 101 |

| 10.5 Fund | ctional Description                    | 103 |

| 10.5.1    | DMA and FMI Global Control             |     |

| 10.5.2    | NAND Flash                             |     |

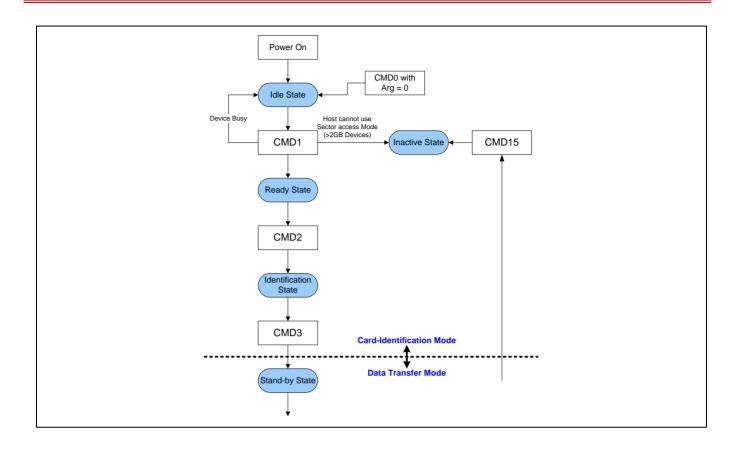

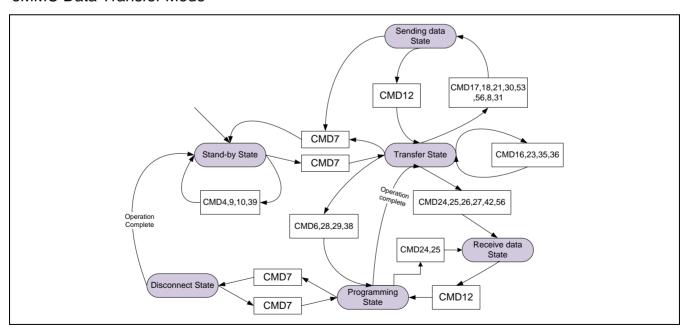

| 10.5.3    | eMMC                                   | 107 |

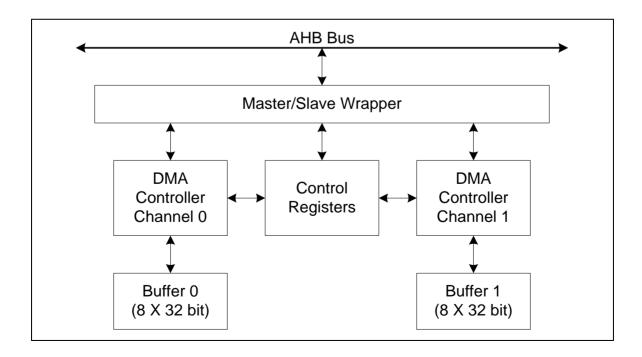

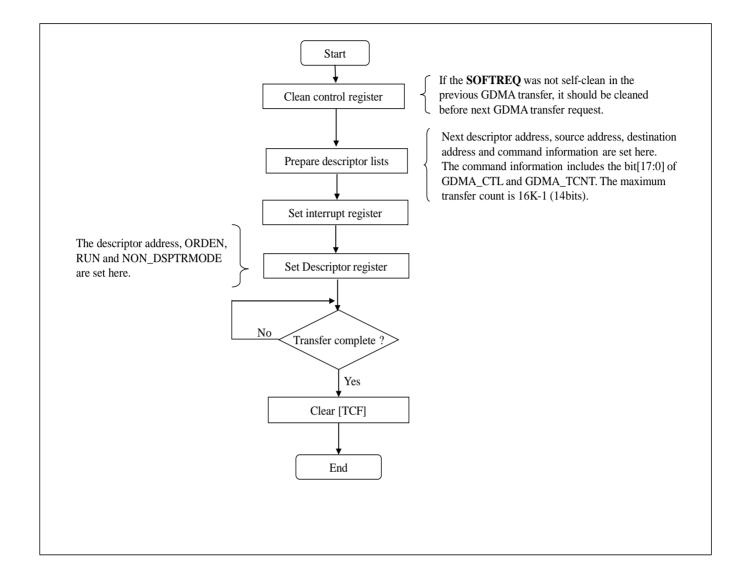

| 11 GENE   | RAL DMA CONTROLLER (GDMA)              | 112 |

| 11.1 Over | rview                                  | 112 |

| 11.2 Feat | ures                                   | 112 |

| 11.3 Bloc | k Diagram                              | 112 |

| 11.4 Regi | ister Map                              | 113 |

| 11.5 Fund | ctional Description                    | 114 |

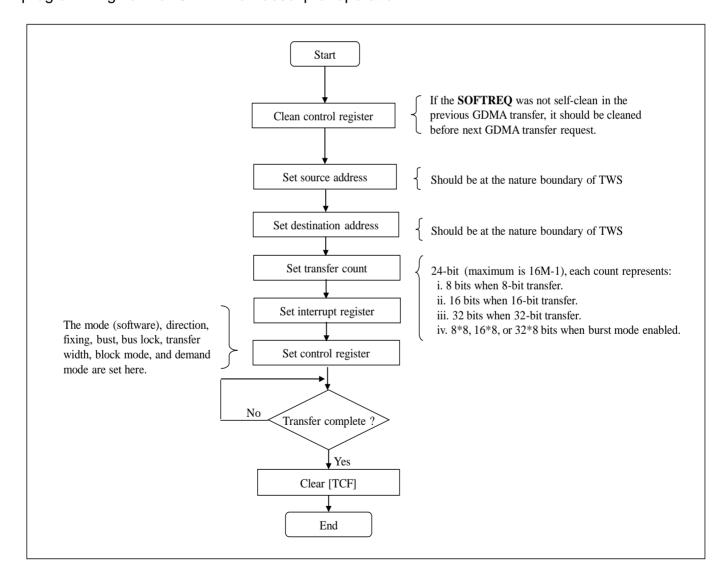

| 11.5.1    | Non-Descriptor Functional Descriptions | 114 |

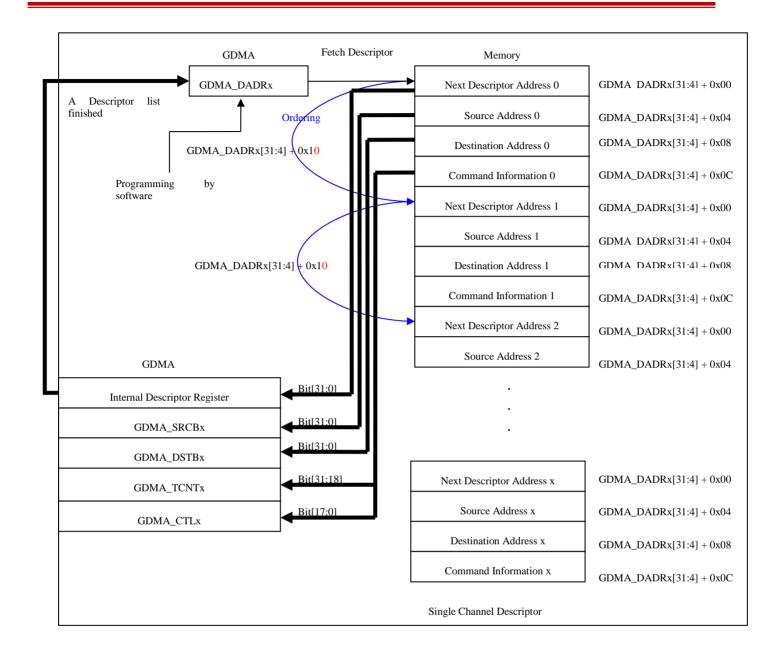

| 11.5.2    | Descriptor Functional Descriptions     | 118 |

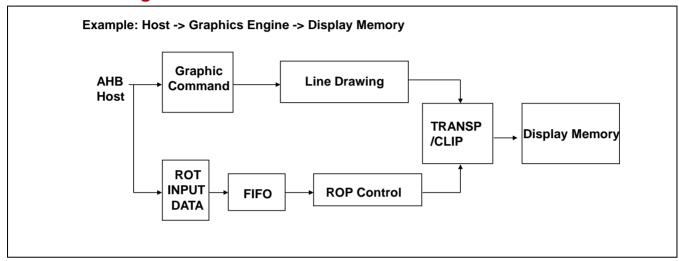

| 12 2D GR  | RAPHIC ENGINE (GE2D)                   | 122 |

|           | rview                                  |     |

|           | ures                                   |     |

|           | k Diagram                              |     |

|           | ister Map                              |     |

| J         | ction Description                      |     |

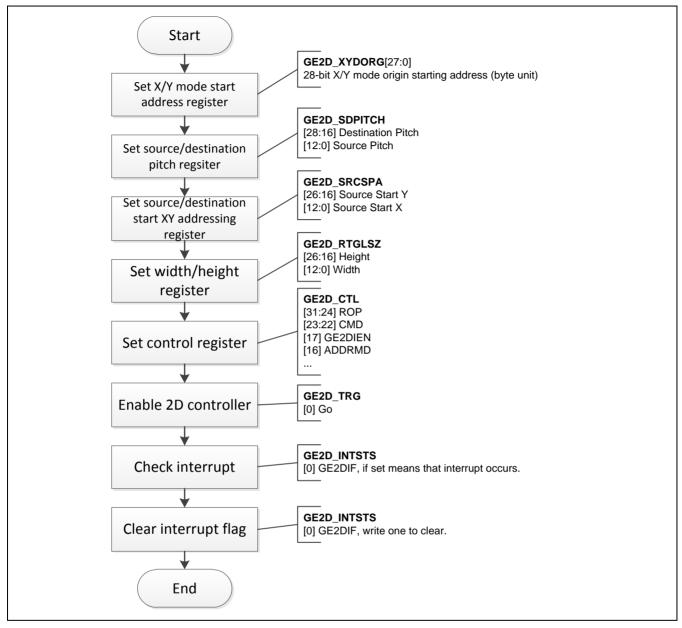

| 12.5.1    | 2D Graphic Engine Initialization       |     |

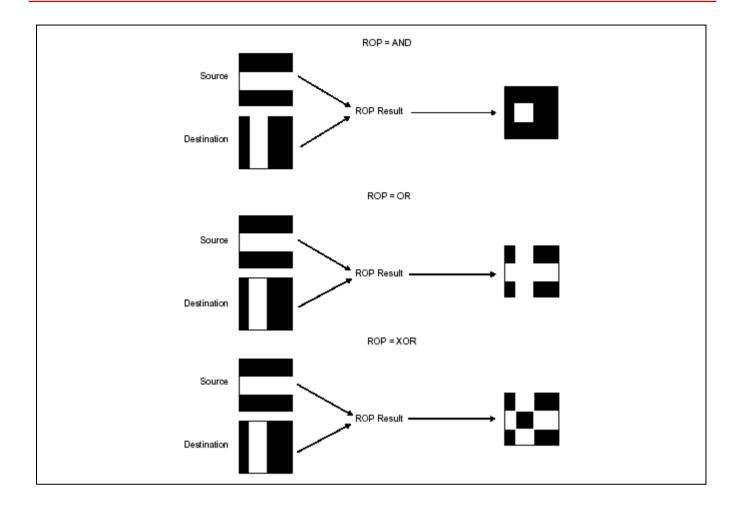

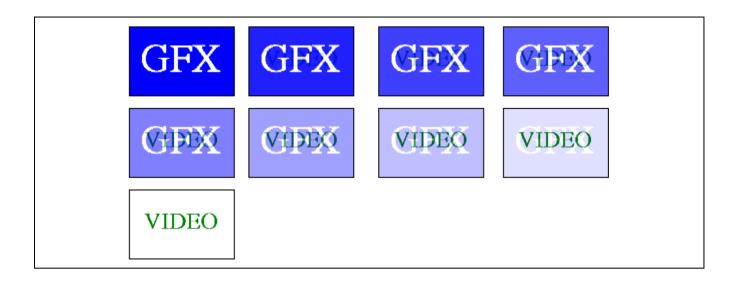

| 12.5.2    | Ternary Raster Operations (ROP)        |     |

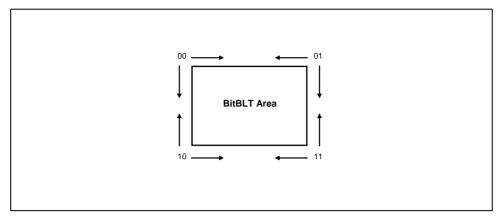

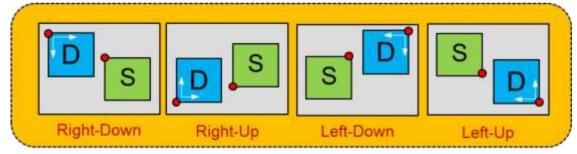

| 12.5.3    | Bit Block Transfer (BitBLT)            |     |

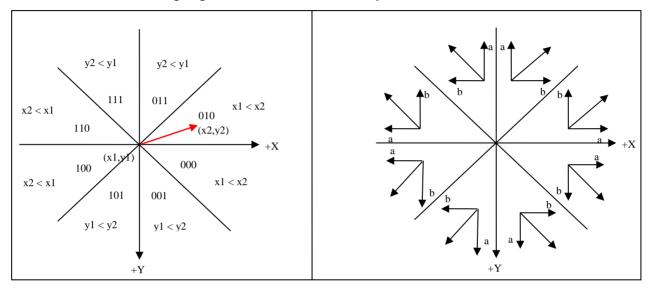

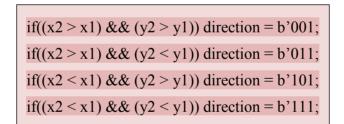

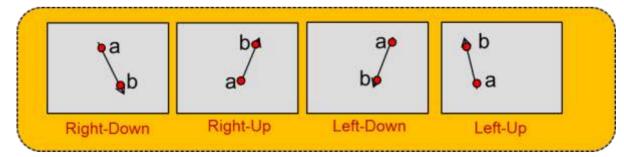

| 12.5.4    | Bresenham Line Drawing                 | 131 |

| 12.5.5    | α Blending                             | 135 |

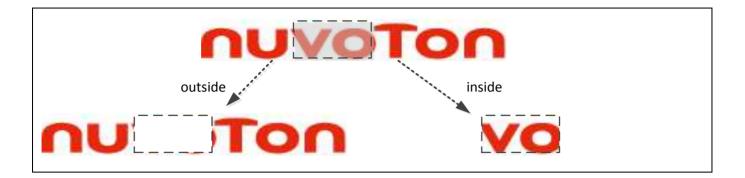

| 12.5.6    | Clipping                               |     |

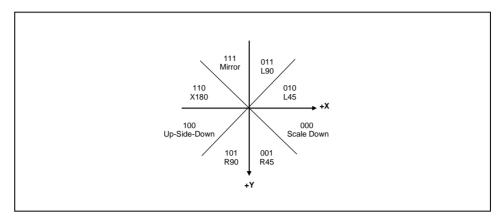

| 12.5.7    | Rotation                               |     |

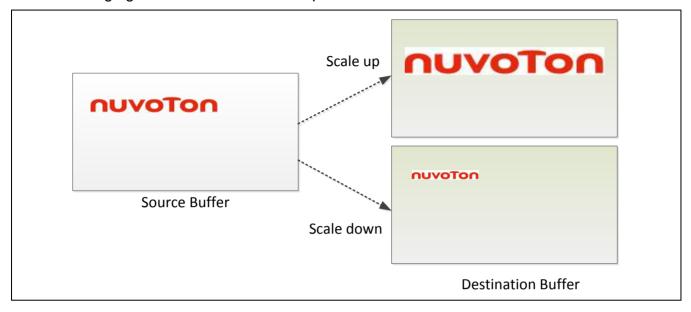

| 12.5.8    | Scale Up/Down                          | 138 |

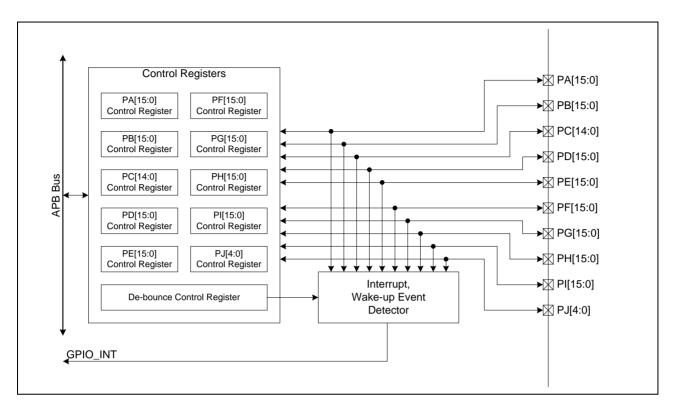

| 13 GENE   | RAL-PURPOSE INPUT/OUTPUT (GPIO)        | 141 |

| 13.1 Over | rview                                  | 141 |

| 13.2 Feat | ures                                   | 141 |

| 13.3 Bloc | k Diagram                              | 141 |

| 13.4 Regi | ister Map                              | 142 |

| 13.5 Fund | ctional Description                    | 146 |

| 13.5.1    | Multiple function pin Configuration    | 146 |

| 13.5.2    | GPIO Output Mode                       |     |

| 13.5.3    | GPIO Input Mode                        |     |

| 13.5.4    | GPIO Interrupt                         | 148 |

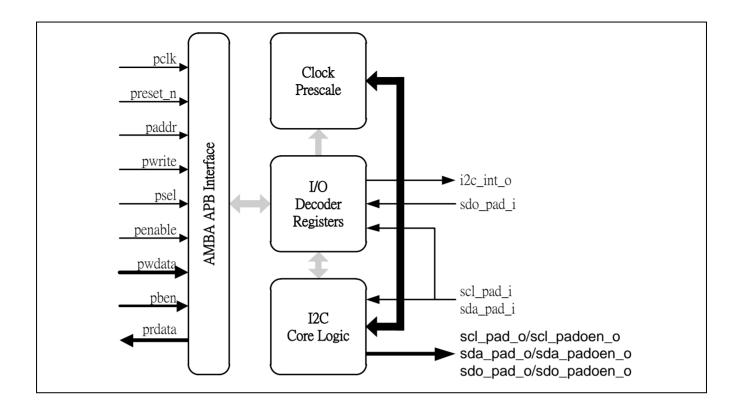

|                   | 14 I <sup>2</sup> C |                                                               | 150 |

|-------------------|---------------------|---------------------------------------------------------------|-----|

|                   | 14.1 Ove            | erview                                                        | 150 |

|                   | 14.2 Feat           | tures                                                         | 150 |

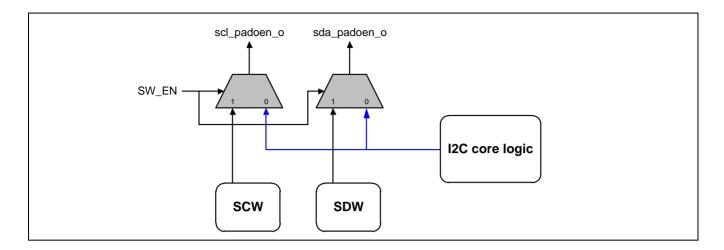

|                   |                     | ction Block                                                   |     |

|                   |                     | ister Map                                                     |     |

|                   | J                   | •                                                             |     |

|                   | 14.5 Fun            | ction Description                                             |     |

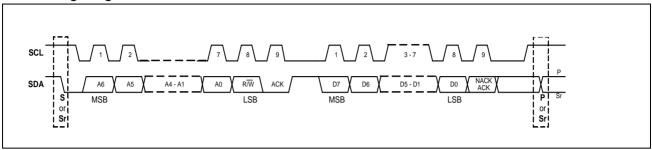

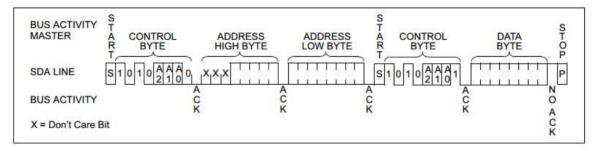

|                   | 14.5.1              | I <sup>2</sup> C Protocol                                     |     |

|                   | 14.5.2              | Data Transmission Continuously                                |     |

|                   | 14.5.3              | Interrupt                                                     |     |

|                   | 14.5.4<br>14.5.5    | Software Mode  I <sup>2</sup> C Operation Using CMDR Register |     |

|                   | 14.5.6              | I <sup>2</sup> C EEPROM Operation Example                     |     |

|                   | 14.0.0              | TO LET NOW Operation Example                                  | 134 |

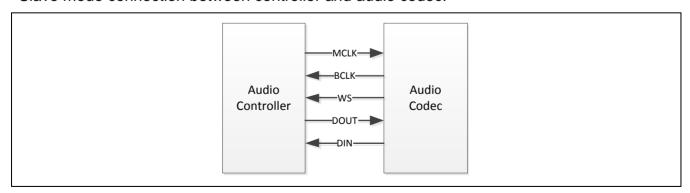

|                   | 15 I <sup>2</sup> S |                                                               | 156 |

|                   | 15.1 Ove            | erview                                                        | 156 |

|                   | 15 2 Feat           | tures                                                         | 156 |

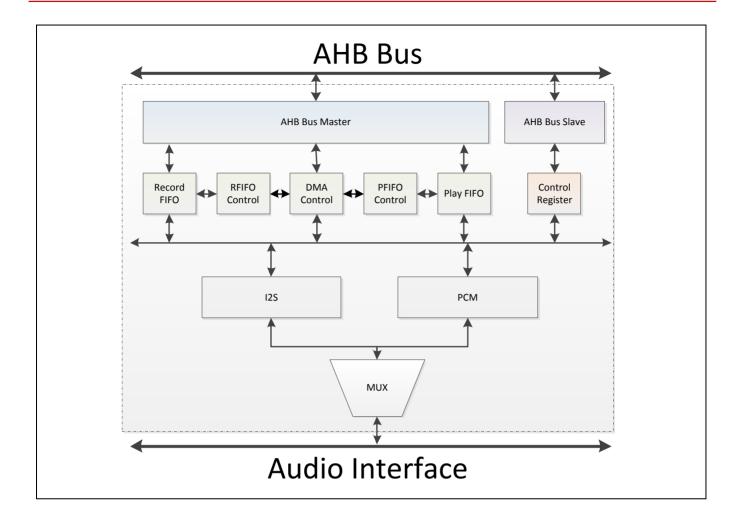

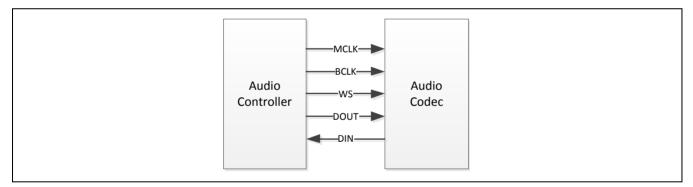

|                   |                     | ction Block                                                   |     |

|                   |                     |                                                               |     |

| 15.4 Register Map |                     | •                                                             |     |

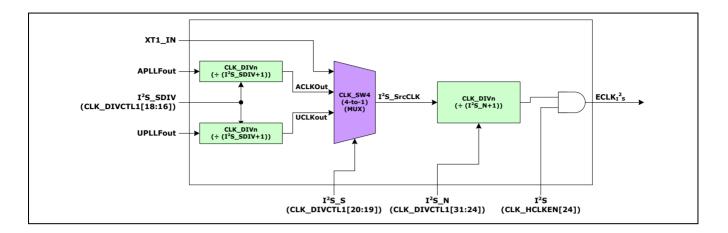

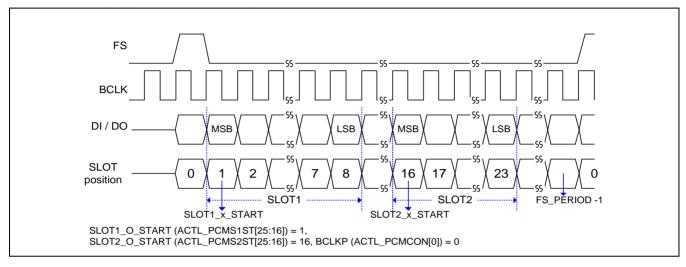

|                   |                     | ctional Description                                           |     |

|                   | 15.5.1              | I <sup>2</sup> S Master/Slave Mode                            |     |

|                   | 15.5.2              | I <sup>2</sup> S Source Clock Configuration                   |     |

|                   | 15.5.3              | I <sup>2</sup> S Calculation and Configuration of Clock       |     |

|                   | 15.5.4              | DMA                                                           |     |

|                   | 15.5.5<br>15.5.6    | Sequence of DMA Data                                          |     |

|                   | 15.5.6              | Interface SelectionPCM Interface                              |     |

|                   | 15.5.8              | Data Split                                                    |     |

|                   | 10.0.0              |                                                               | 103 |

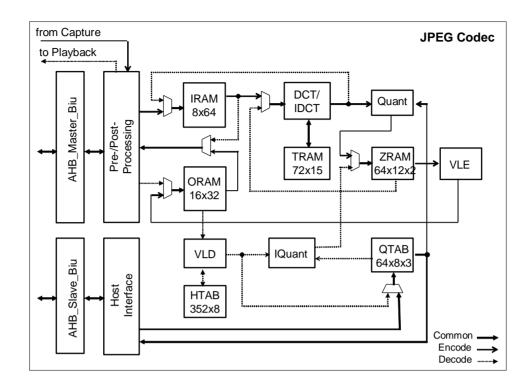

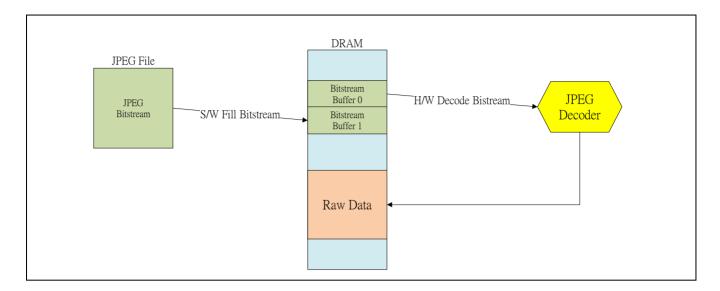

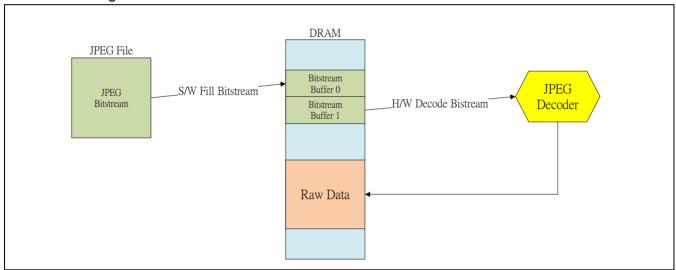

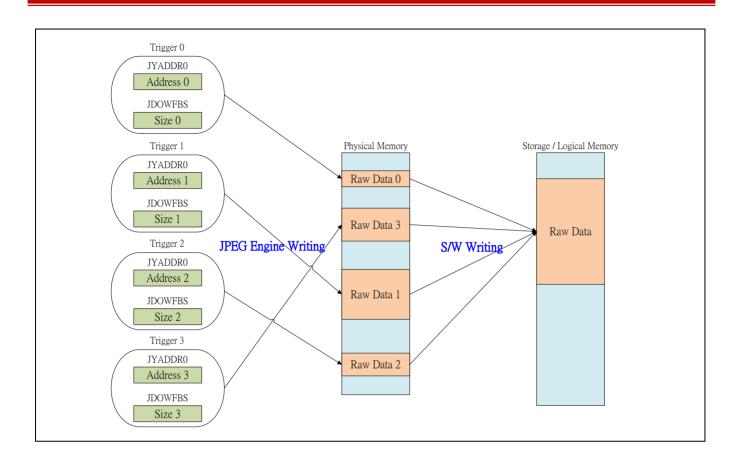

|                   | 16 JPEG             | CODEC                                                         | 164 |

|                   | 16.1 Ove            | erview                                                        | 164 |

|                   | 16.2 Feat           | ture                                                          | 164 |

|                   | 16.3 Bloc           | ck Diagram                                                    | 164 |

|                   | 16.4 Reg            | jister Map                                                    | 165 |

|                   | 16.5 Fun            | ctional Description                                           | 167 |

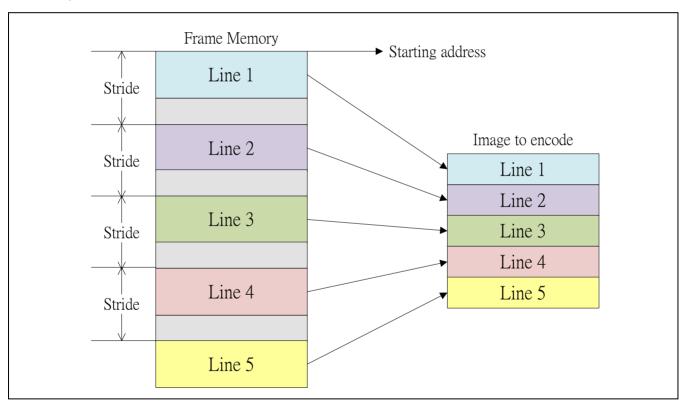

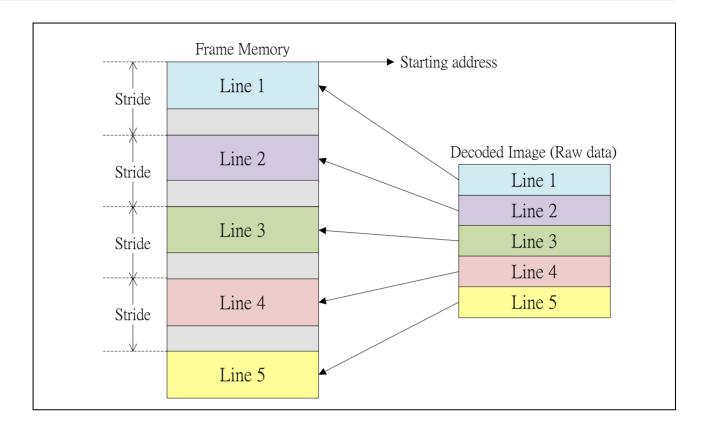

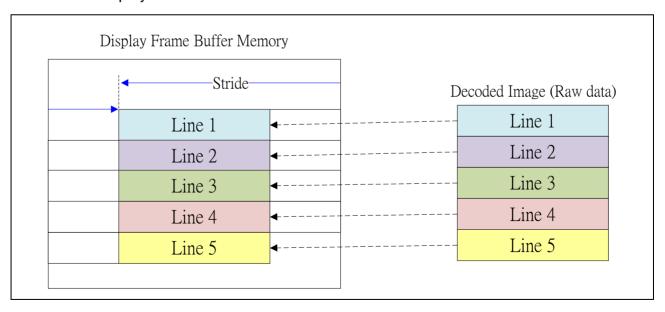

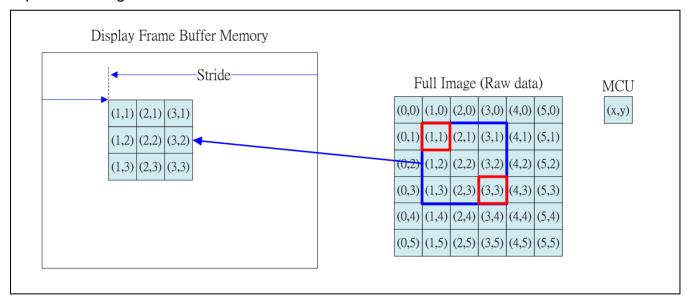

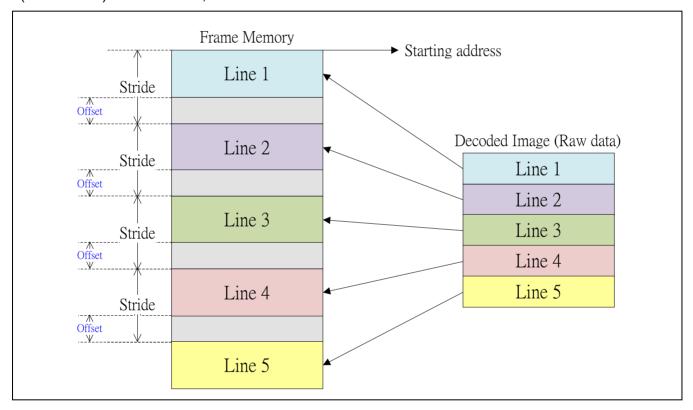

|                   | 16.5.1              | Memory Access                                                 | 167 |

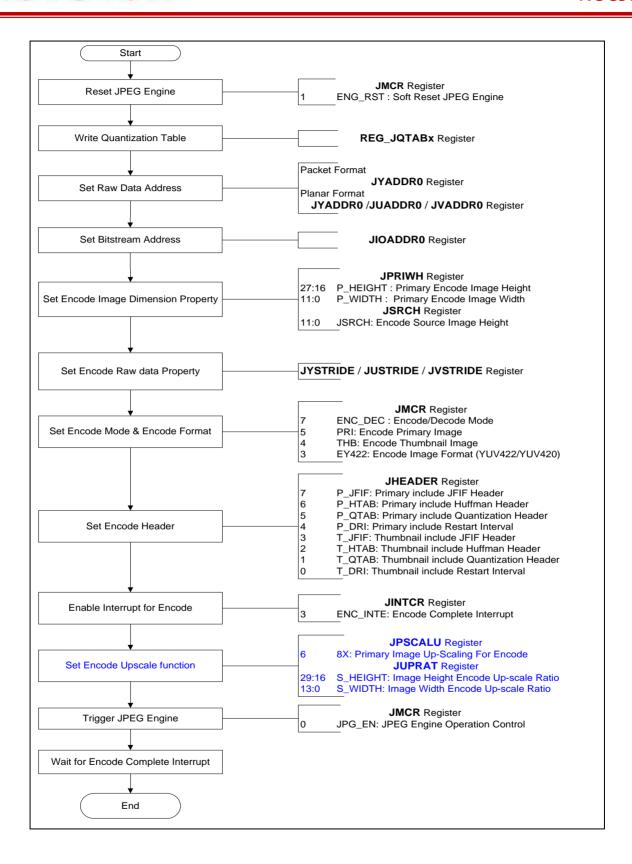

|                   | 16.5.2              | JPEG Encoding                                                 |     |

|                   | 16.5.3              | Normal Encoding                                               |     |

|                   | 16.5.4              | Encoding Scaling up                                           |     |

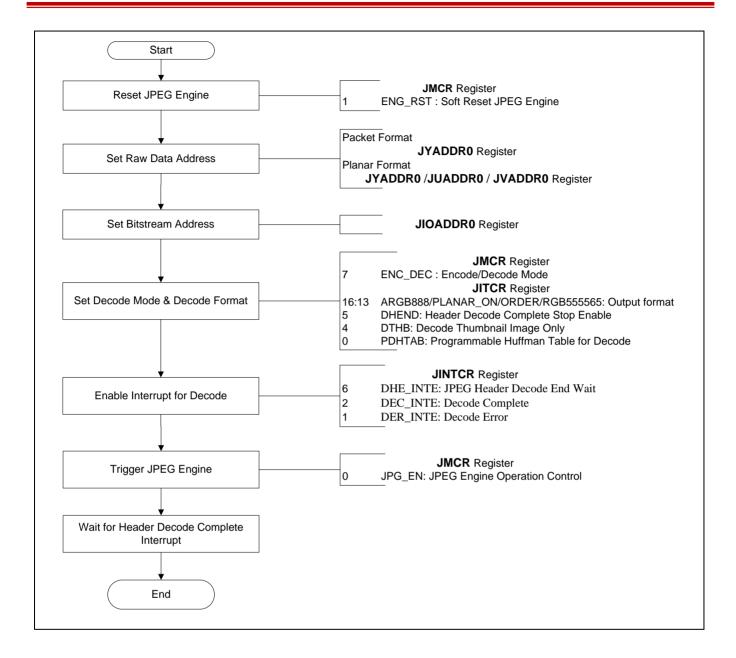

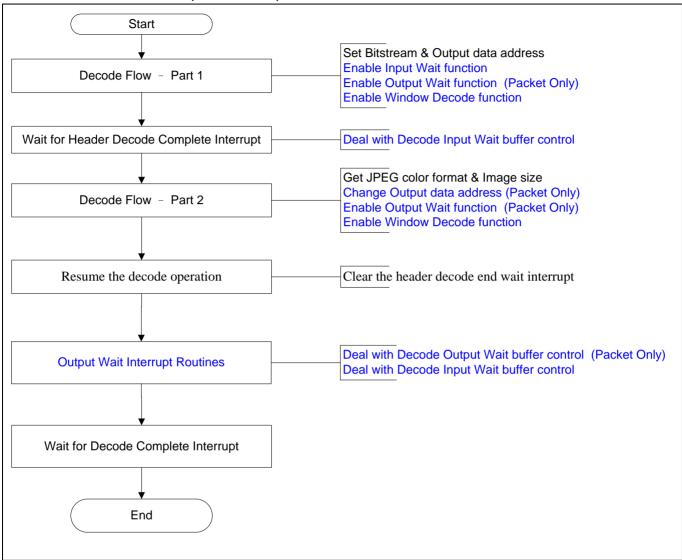

|                   | 16.5.5              | JPEG Decoding                                                 | 173 |

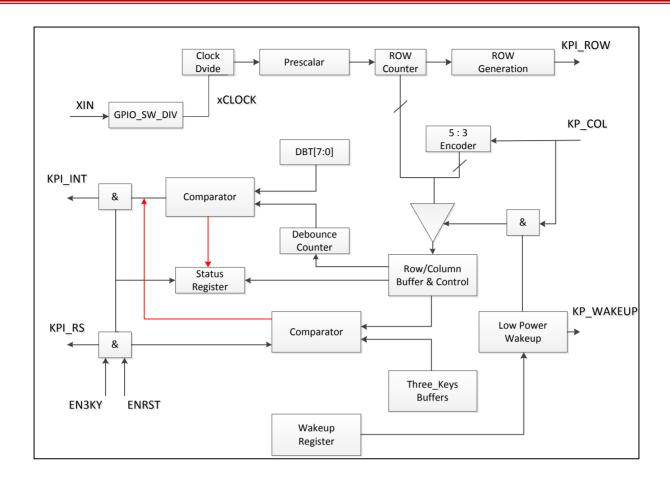

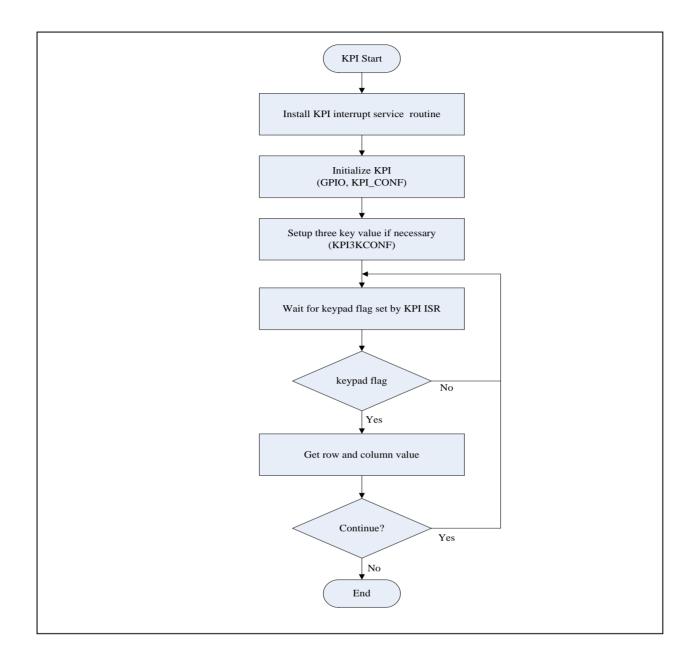

| 17 | ' KEYP                                                                                                                                         | AD INTERFACE                                                   | 181        |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|

|    | 17.1 Over                                                                                                                                      | view                                                           | 181        |

|    | 17.2 Feat                                                                                                                                      | ures                                                           | 181        |

|    | 17.3 Bloc                                                                                                                                      | k Diagram                                                      | 181        |

|    |                                                                                                                                                | ster Map                                                       |            |

|    | _                                                                                                                                              | tional Description                                             |            |

|    | 17.5.1                                                                                                                                         | Keypad Controller Configuration                                |            |

|    | 17.5.2                                                                                                                                         | Wake UP Function                                               |            |

|    |                                                                                                                                                |                                                                |            |

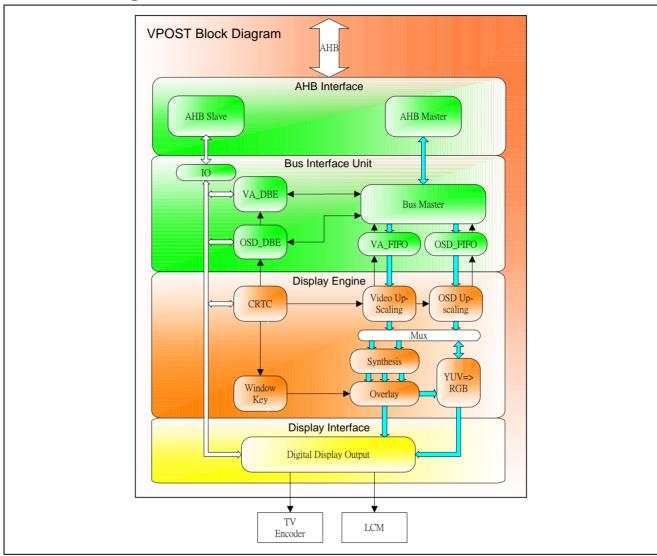

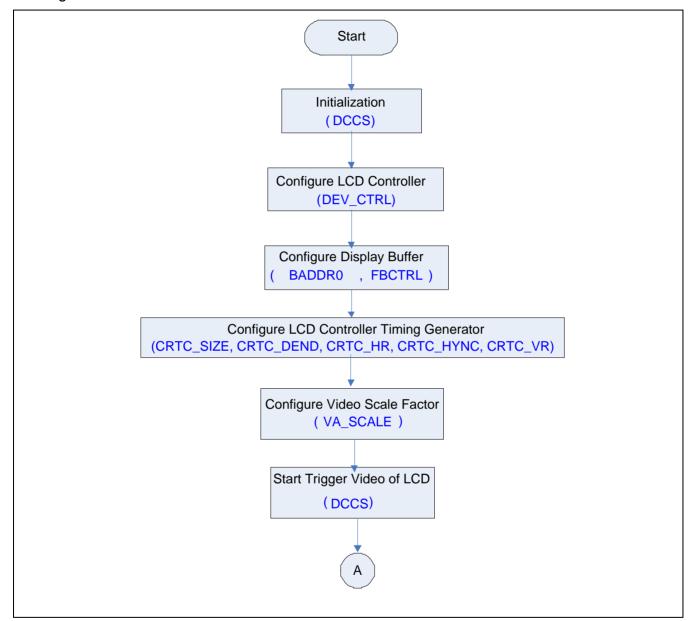

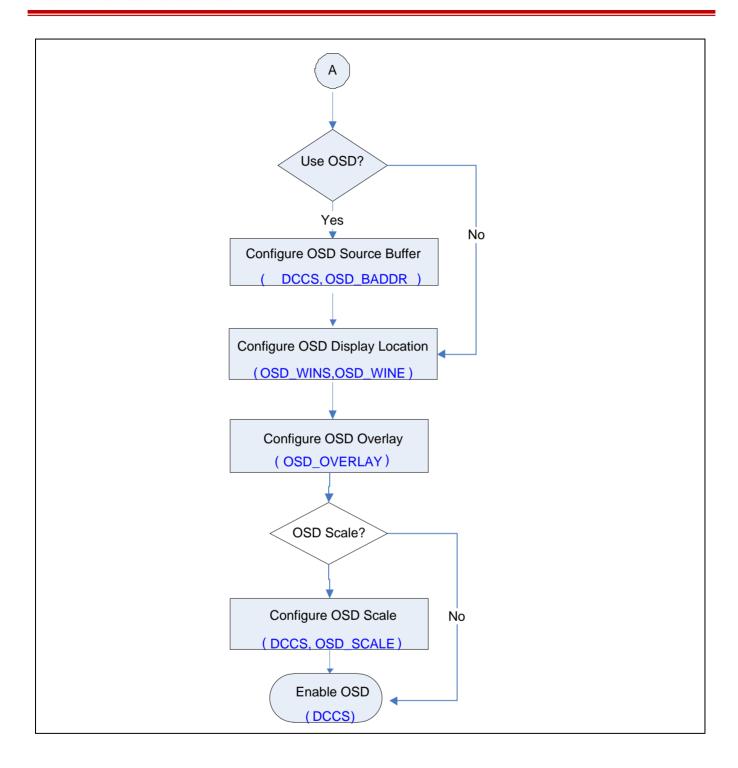

| 18 |                                                                                                                                                | ISPLAY INTERFACE CONTROLLER (LCM)                              |            |

|    | 18.1 Over                                                                                                                                      | view                                                           | 185        |

|    | 18.2 Feat                                                                                                                                      | ures                                                           | 185        |

|    | 18.3 Bloc                                                                                                                                      | k Diagram                                                      | 186        |

|    | 18.4 Regi                                                                                                                                      | ster Map                                                       | 186        |

|    | 18.5 Fund                                                                                                                                      | ctional Description                                            | 187        |

|    | 18.5.1                                                                                                                                         | LCD Configuration Flow                                         |            |

|    | 18.5.2<br>18.5.3                                                                                                                               | LCD Controller Initialization and Configuration                |            |

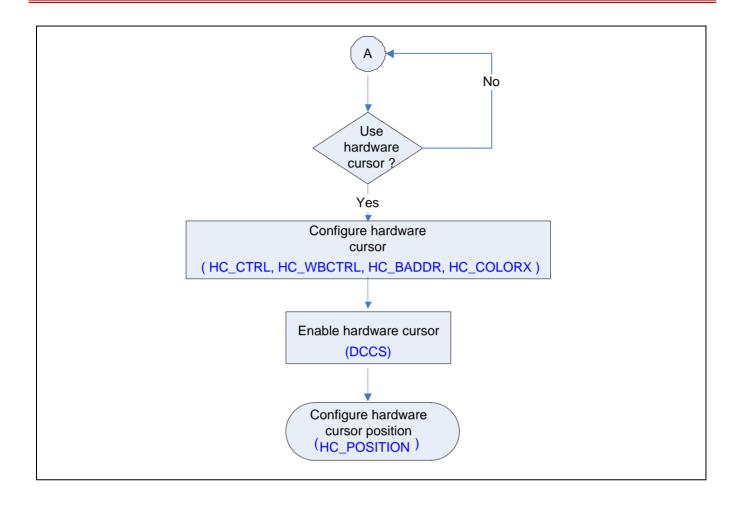

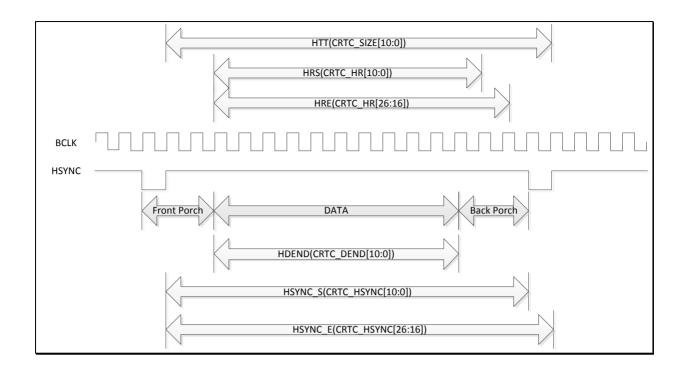

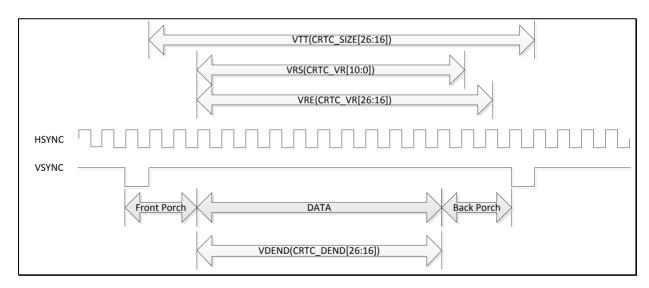

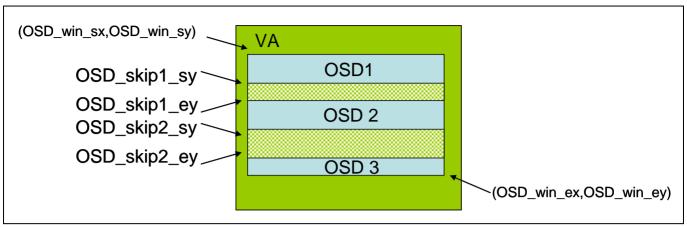

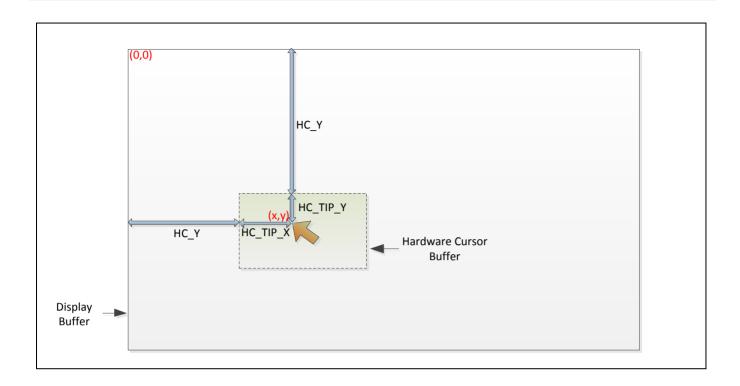

|    | 18.5.4                                                                                                                                         | Hardware Cursor                                                |            |

|    |                                                                                                                                                |                                                                |            |

|    |                                                                                                                                                |                                                                |            |

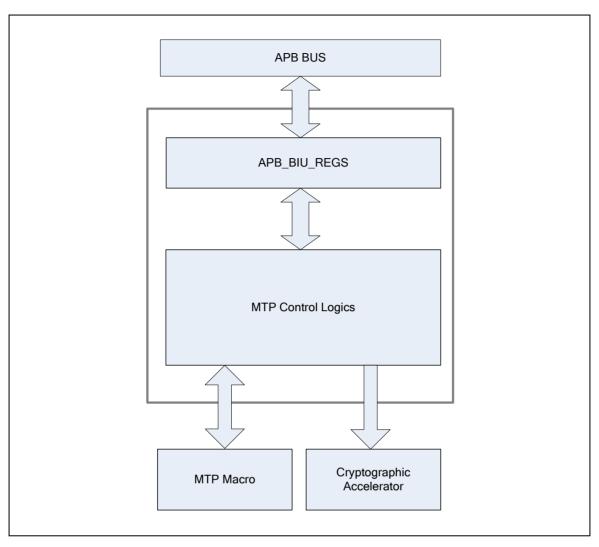

| 19 | MTP C                                                                                                                                          | ONTROLLER                                                      | 195        |

| 19 |                                                                                                                                                | view                                                           |            |

| 19 | 19.1 Over                                                                                                                                      |                                                                | 195        |

| 19 | 19.1 Over                                                                                                                                      | view                                                           | 195<br>195 |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc                                                                                                            | viewures                                                       |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi                                                                                               | viewuresk Diagram                                              |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi                                                                                               | viewk Diagramster Map                                          |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2                                                              | viewk Diagramster Map  ctional Description  Use MTP Controller |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3                                                    | viewk Diagramster Map  Use MTP Controller                      |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4                                          | view                                                           |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3                                                    | view                                                           |            |

| 19 | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4<br>19.5.5                                | view                                                           |            |

| 19 | 19.1 Over<br>19.2 Feats<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4<br>19.5.5<br>19.5.6                     | view                                                           |            |

| 20 | 19.1 Over<br>19.2 Feats<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4<br>19.5.5<br>19.5.6<br>19.5.7<br>19.5.8 | view                                                           |            |

|    | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4<br>19.5.5<br>19.5.6<br>19.5.7<br>19.5.8  | view                                                           |            |

|    | 19.1 Over<br>19.2 Feat<br>19.3 Bloc<br>19.4 Regi<br>19.5 Fund<br>19.5.1<br>19.5.2<br>19.5.3<br>19.5.4<br>19.5.5<br>19.5.6<br>19.5.7<br>19.5.8  | wiew                                                           |            |

|   | 20.4 Regi        | ster Map                                                        | 204 |

|---|------------------|-----------------------------------------------------------------|-----|

|   | 20.5 Fund        | ctional Description                                             | 205 |

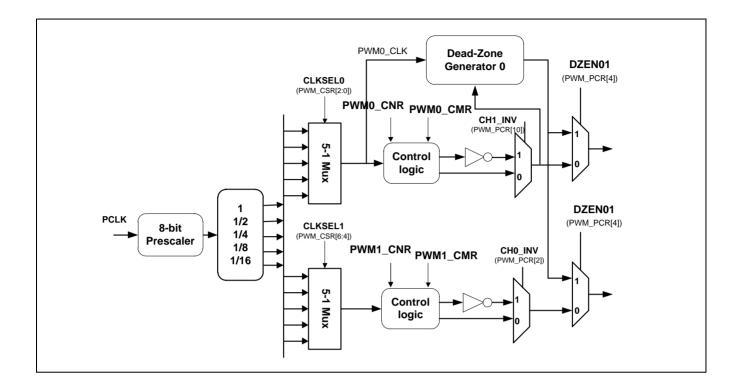

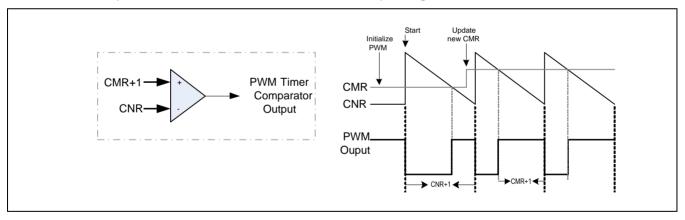

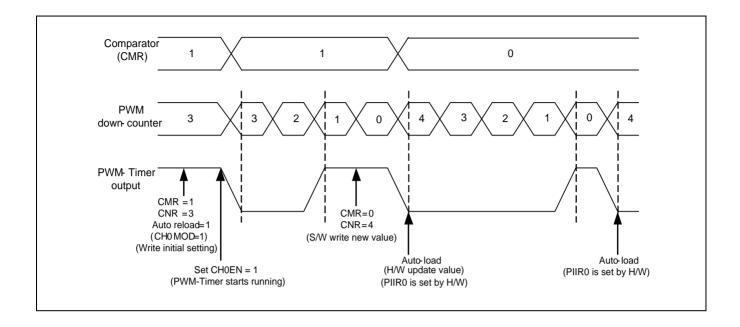

|   | 20.5.1           | PWM Timer Operation                                             | 205 |

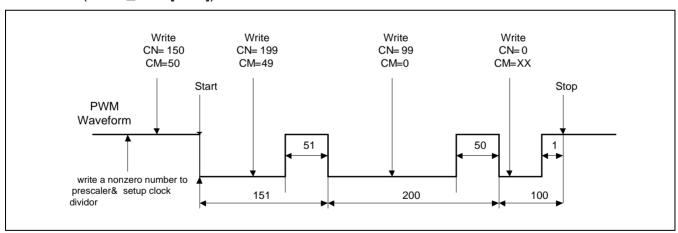

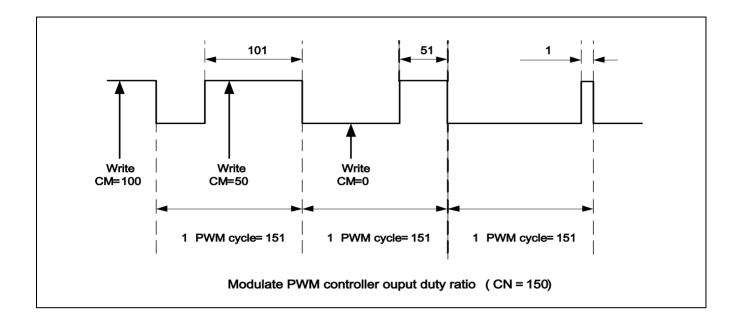

|   | 20.5.2           | PWM double buffer                                               | 206 |

|   | 20.5.3           | Periodic and One-Shot Operation                                 | 207 |

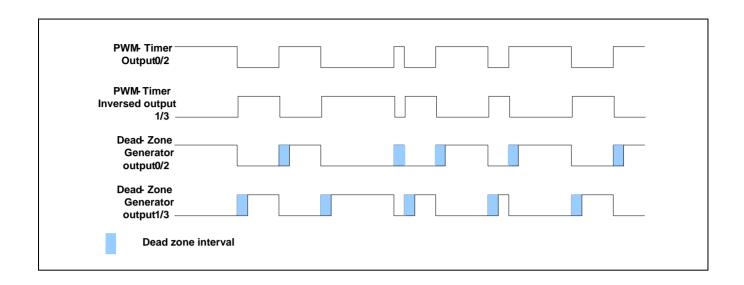

|   | 20.5.4           | Dead-Zone Generator                                             |     |

|   | 20.5.5           | PWM Timer Start Procedure                                       |     |

|   | 20.5.6           | PWM Timer Stop Procedure                                        | 209 |

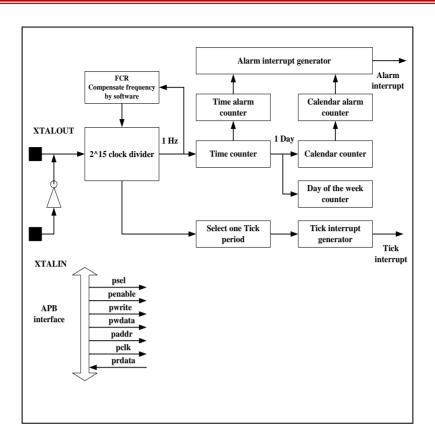

| 2 | 1 REAL           | TIME CLOCK (RTC)                                                | 210 |

|   | 21.1 Over        | rview                                                           | 210 |

|   | 21.2 Feat        | ures                                                            | 210 |

|   | 21.3 Bloc        | k Diagram                                                       | 210 |

|   | 21.4 Regi        | ster Map                                                        | 211 |

|   | 21.5 Fund        | ctional Description                                             | 212 |

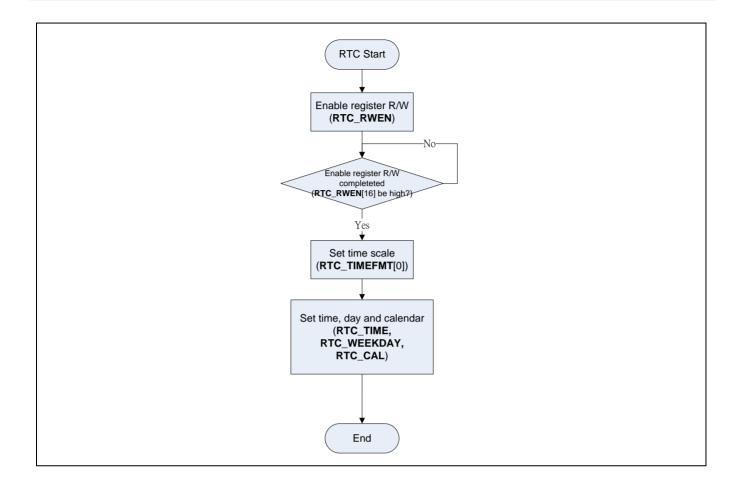

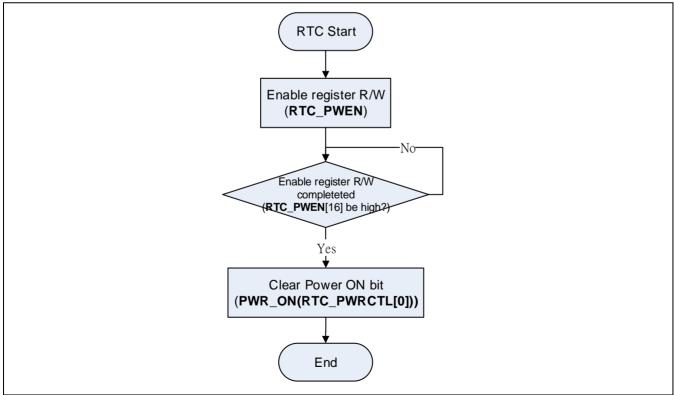

|   | 21.5.1           | RTC Initiation                                                  | 212 |

|   | 21.5.2           | RTC write enable                                                | 212 |

|   | 21.5.3           | 12/24 hour Time scale selection                                 | 213 |

|   | 21.5.4           | Set Calendar and Time                                           | 213 |

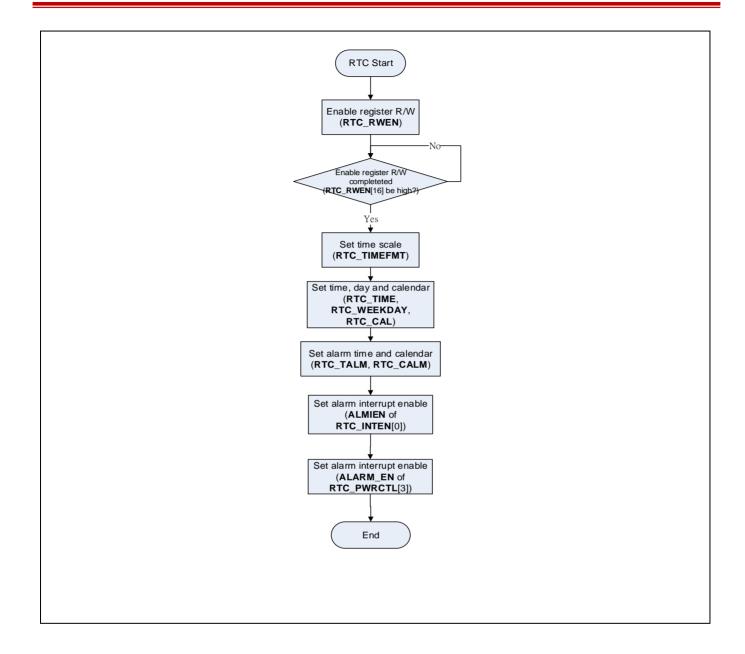

|   | 21.5.5           | Set Calendar and Time Alarm (Absolute)                          | 214 |

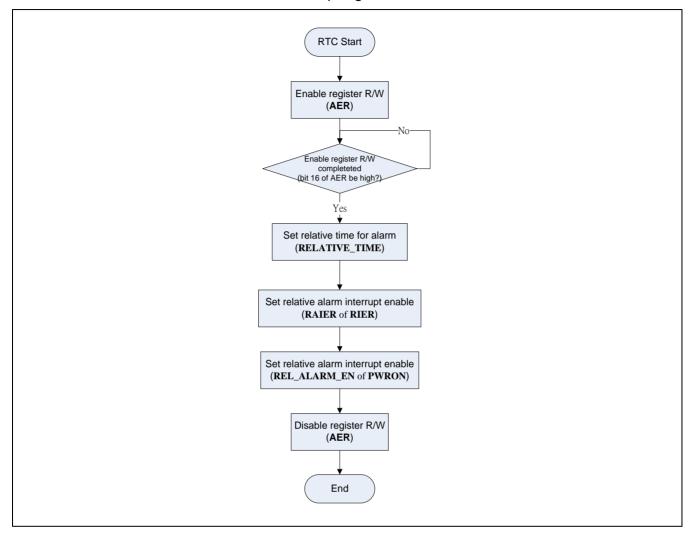

|   | 21.5.6           | Set Time Alarm (Relative)                                       | 215 |

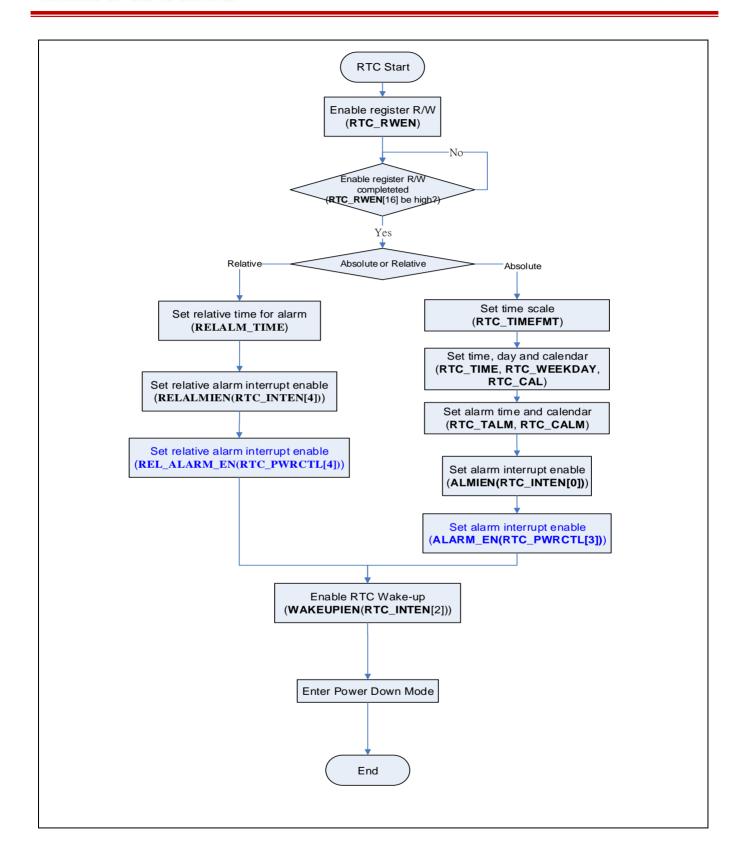

|   | 21.5.7           | Set wake-up function                                            |     |

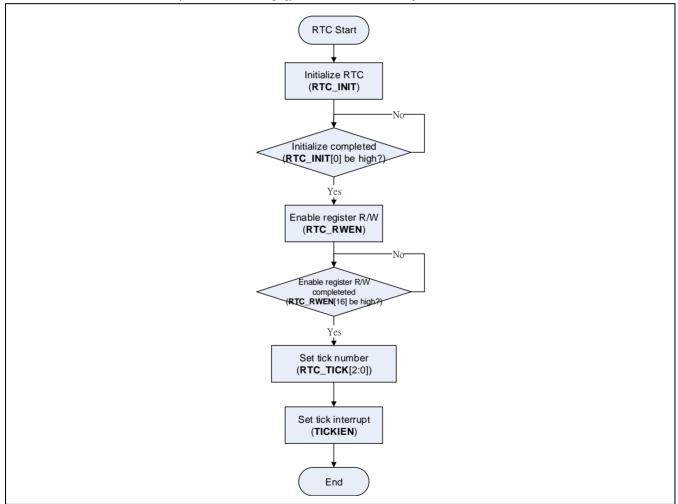

|   | 21.5.8           | Set tick interrupt                                              |     |

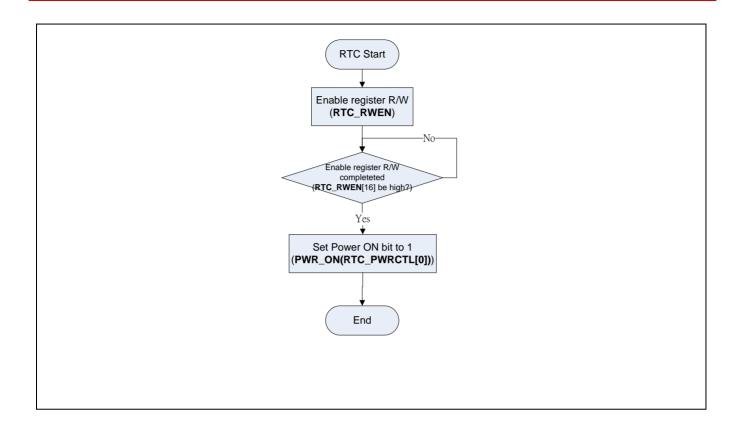

|   | 21.5.9           | System Power Control Flow                                       |     |

|   | 21.5.10          | Frequency Compensation:                                         | 224 |

| 2 | 2 SMAR           | T CARD HOST INTERFACE (SC)                                      | 226 |

|   | 22.1 Over        | rview                                                           | 226 |

|   | 22.2 Feat        | ures                                                            | 226 |

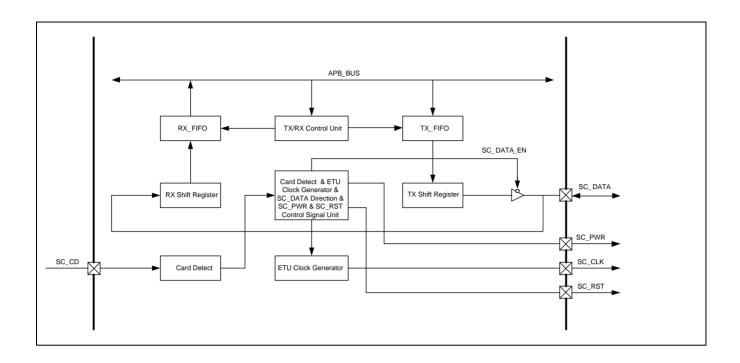

|   | 22.3 Bloc        | k Diagram                                                       | 226 |

|   | 22.4 Regi        | ster Map                                                        | 227 |

|   | 22.5 Fund        | ctional Description                                             | 228 |

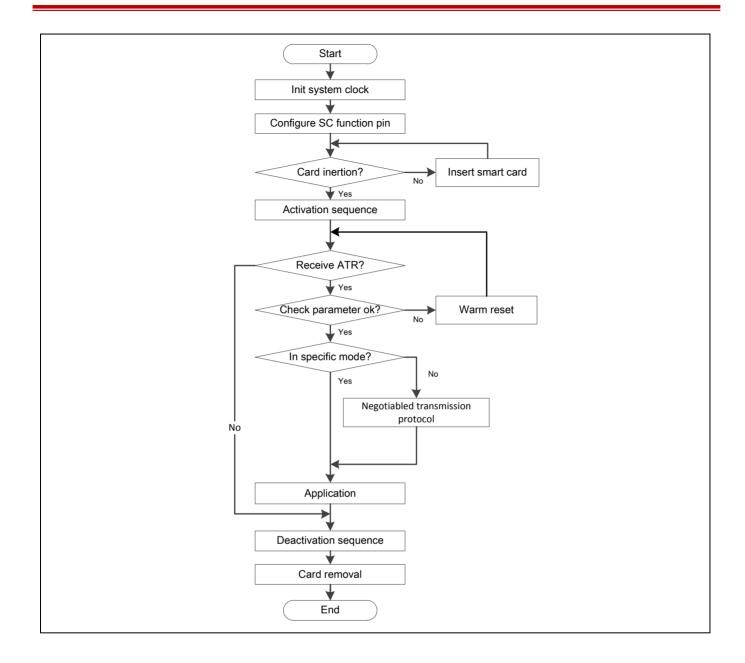

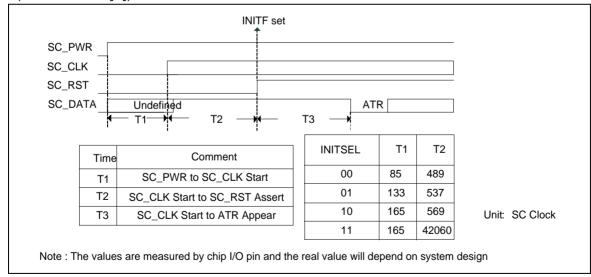

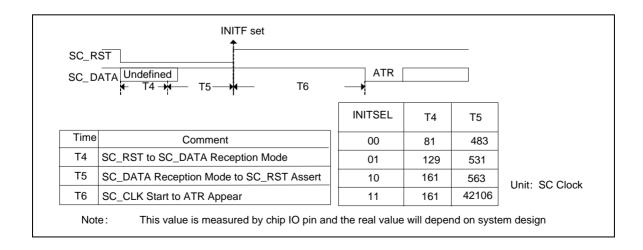

|   | 22.5.1           | Activation (Cold Reset)                                         |     |

|   | 22.5.2           | Warm Reset                                                      |     |

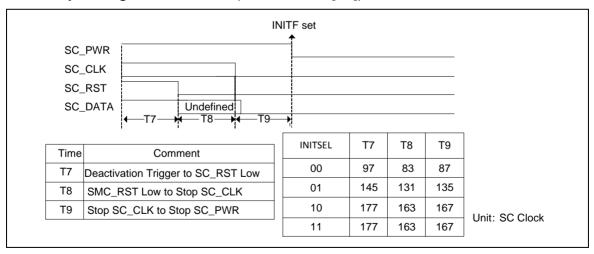

|   | 22.5.3           | Deactivation                                                    |     |

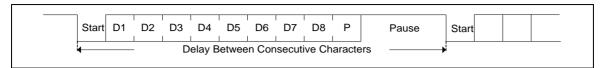

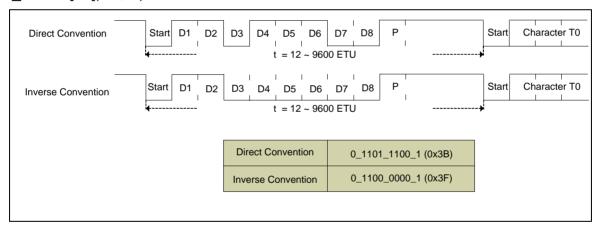

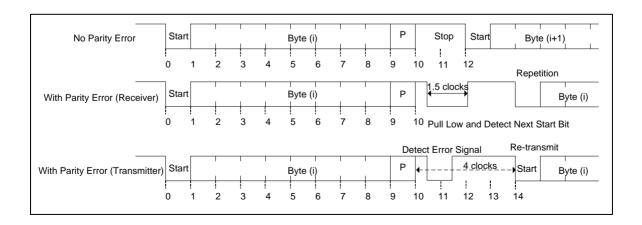

|   | 22.5.4           | Data Format                                                     |     |

|   | 22.5.5           | Data Transfer                                                   |     |

|   | 22.5.6           | Error Signal and Character Repetition Internal Time-out Counter |     |

|   | 22.5.7<br>22.5.8 | Smartcard Insert/Remove Detection                               |     |

|   | 22.5.8<br>22.5.9 | Miscellaneous Transmission Settings                             |     |

|   | 22.5.9           | g ·                                                             |     |

|   | 22.3.10          | G/TIXT IVIOUG                                                   | 237 |

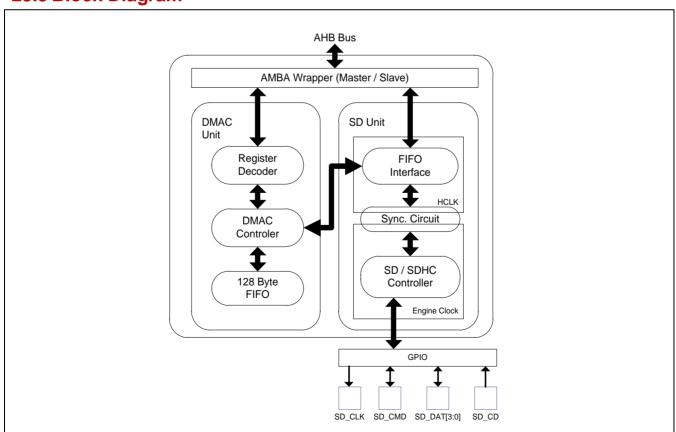

| 2 | 3 SECUI          | RE DIGITAL HOST CONTROLLER (SDH)                                | 239 |

|    | 23.1 Ove         | rview                          | 239 |

|----|------------------|--------------------------------|-----|

|    | 23.2 Feat        | ures                           | 239 |

|    | 23.3 Bloc        | k Diagram                      | 239 |

|    |                  | ister Map                      |     |

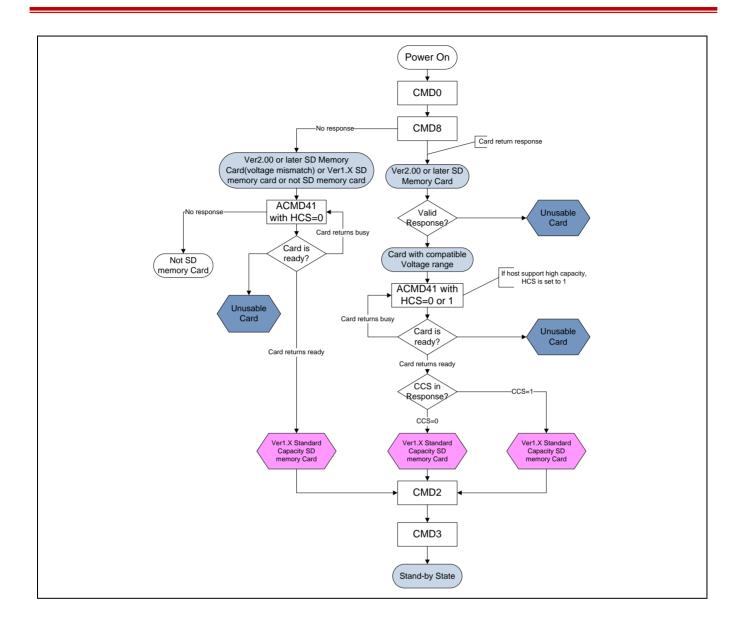

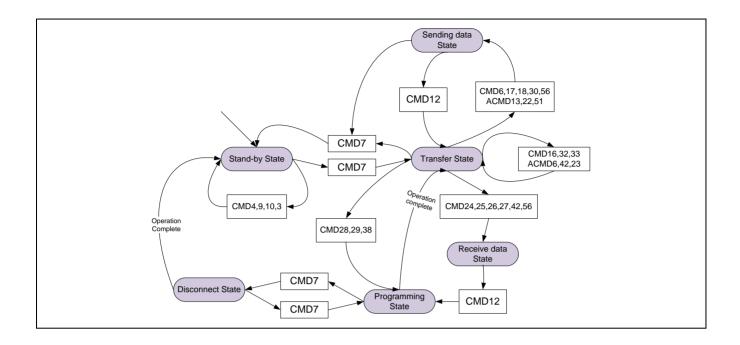

|    | •                | ctional Description            |     |

|    |                  | •                              |     |

|    | 23.5.1<br>23.5.2 | Global ControlSend Command     |     |

|    | 23.5.2           | Get Response                   |     |

|    | 23.5.4           | Read SD Card                   |     |

|    | 23.5.5           | Write SD Card                  |     |

| 24 | SPI              |                                | 246 |

|    | 24.1 Ove         | rview                          | 246 |

|    | 24.2 Feat        | ures                           | 246 |

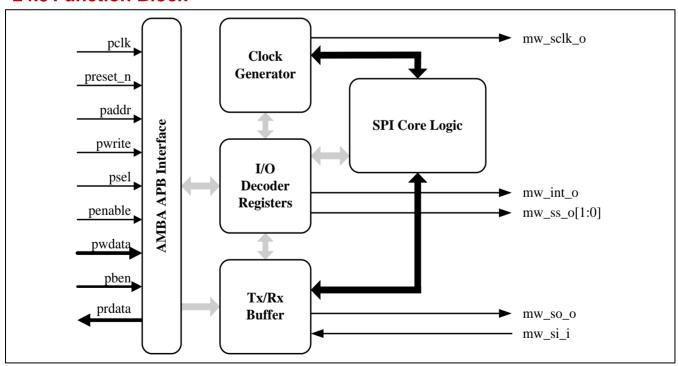

|    | 24.3 Fund        | ction Block                    | 246 |

|    | 24.4 Regi        | ister Map                      | 246 |

|    | •                | ction Description              |     |

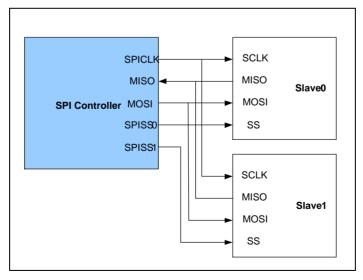

|    | 24.5.1           | Slave Selection                |     |

|    | 24.5.2           | Automatic Slave Select         |     |

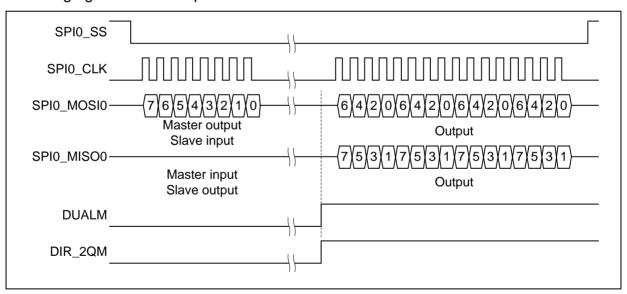

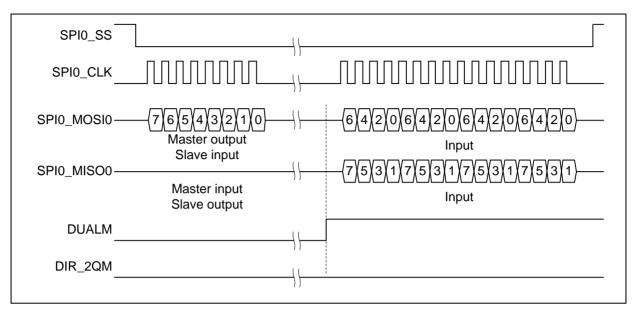

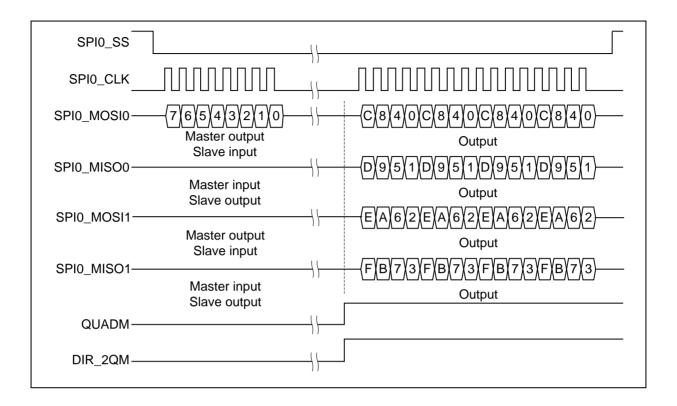

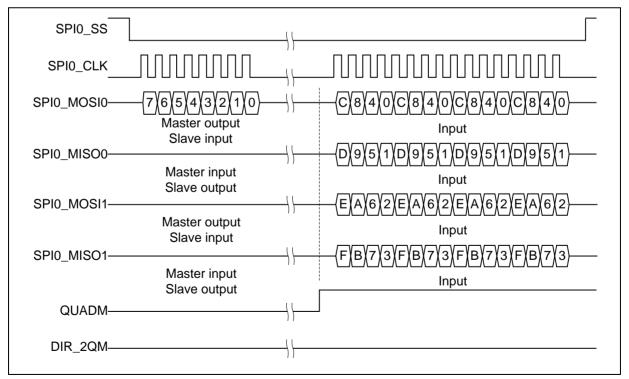

|    | 24.5.3           | Dual / Quad Mode               | 248 |

|    | 24.5.4           | Burst Mode                     |     |

|    | 24.5.5           | SPI Interrupt                  |     |

|    | 24.5.6           | SPI Programming Example        | 251 |

| 25 | TIMER            | CONTROLLER                     | 253 |

|    | 25.1 Ove         | rview                          | 253 |

|    | 25.2 Feat        | ures                           | 253 |

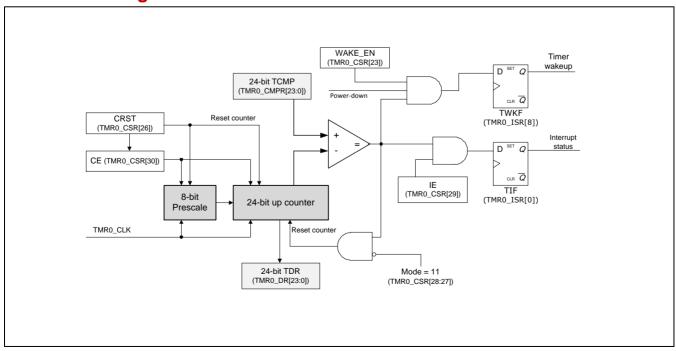

|    | 25.3 Bloc        | k Diagram                      | 253 |

|    | 25.4 Regi        | ister Map                      | 254 |

|    | 25.5 Fund        | ctional Description            | 254 |

|    | 25.5.1           | Timer Initialization           | 254 |

|    | 25.5.2           | Interrupt Handling             |     |

|    | 25.5.3           | Timeout Frequency              |     |

|    | 25.5.4           | One-shot Mode                  |     |

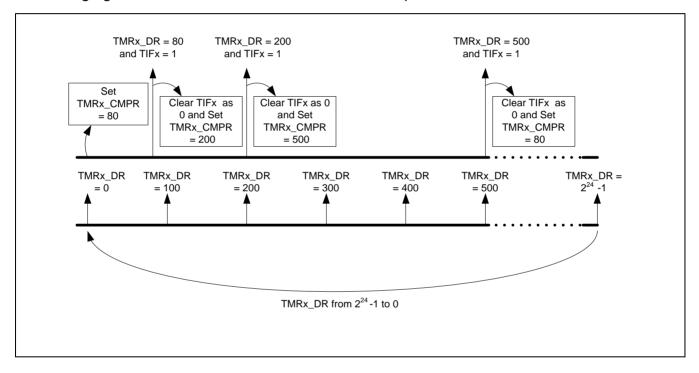

|    | 25.5.5<br>25.5.6 | Periodic Mode  Continuous Mode |     |

|    | 20.0.0           | Continuous Wode                | 230 |

| 26 | UART             |                                | 258 |

|    | 26.1 Ove         | rview                          | 258 |

|    | 26.2 Feat        | ures                           | 260 |

|    | 20.3 DIUC                                                                                                                                                                | k Diagram                                                                                                                                                                              | 260               |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

|    | 26.4 Regi                                                                                                                                                                | ster Map                                                                                                                                                                               | 261               |

|    | 26.5 Fund                                                                                                                                                                | ctional Description                                                                                                                                                                    | 262               |

|    | 26.5.1<br>26.5.2<br>26.5.3<br>26.5.4                                                                                                                                     | InitializationsIrDA ModeRS485 Function ModeLIN (Local Interconnection Network) Mode                                                                                                    | 263<br>264        |

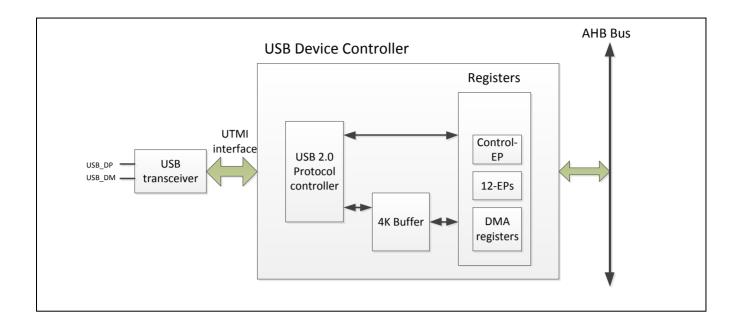

| 27 | USB 2                                                                                                                                                                    | .0 DEVICE CONTROLLER                                                                                                                                                                   | 268               |

|    | 27.1 Over                                                                                                                                                                | view                                                                                                                                                                                   | 268               |

|    | 27.2 Feat                                                                                                                                                                | ures                                                                                                                                                                                   | 268               |

|    | 27.3 Bloc                                                                                                                                                                | k Diagram                                                                                                                                                                              | 268               |

|    | 27.4 Regi                                                                                                                                                                | ster Map                                                                                                                                                                               | 269               |

|    | •                                                                                                                                                                        | tional Description                                                                                                                                                                     |                   |

|    | 27.5.1                                                                                                                                                                   | Initialize                                                                                                                                                                             | 274               |

|    | 27.5.2                                                                                                                                                                   | Interrupt Service Routine                                                                                                                                                              | 275               |

|    | 27.5.3                                                                                                                                                                   | Standard Request                                                                                                                                                                       |                   |

|    | 27.5.4                                                                                                                                                                   | Set Address Request                                                                                                                                                                    |                   |

|    | 27.5.5                                                                                                                                                                   | Get Descriptor                                                                                                                                                                         |                   |

|    | 27.5.6<br>27.5.7                                                                                                                                                         | IN TransmissionOUT Transmission                                                                                                                                                        |                   |

|    |                                                                                                                                                                          |                                                                                                                                                                                        |                   |

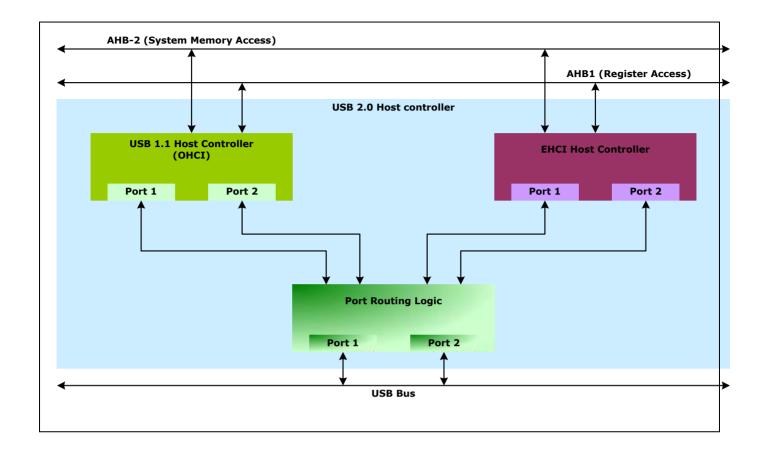

| 28 |                                                                                                                                                                          | IOST CONTROLLER                                                                                                                                                                        |                   |

| 28 | 28.1 Over                                                                                                                                                                | view                                                                                                                                                                                   | 279               |

| 28 | 28.1 Over                                                                                                                                                                | viewures                                                                                                                                                                               | 279<br>279        |

| 28 | 28.1 Over<br>28.2 Feat<br>28.3 Bloc                                                                                                                                      | viewuresk Diagram                                                                                                                                                                      | 279<br>279<br>279 |

| 28 | 28.1 Over<br>28.2 Feate<br>28.3 Bloc<br>28.3.1                                                                                                                           | viewk Diagram                                                                                                                                                                          | 279279279280      |

| 28 | 28.1 Over<br>28.2 Feat<br>28.3 Bloc                                                                                                                                      | viewuresk Diagram                                                                                                                                                                      |                   |

| 28 | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3                                                                                                       | wiewk Diagram  Basic Configuration  EHCI Controller                                                                                                                                    |                   |

| 28 | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi                                                                                          | wiewk Diagram                                                                                                                                                                          |                   |

| 28 | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi                                                                                          | wiew                                                                                                                                                                                   |                   |

| 28 | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund                                                                             | wiew                                                                                                                                                                                   |                   |

| 28 | 28.1 Over<br>28.2 Feate<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund<br>28.5.1<br>28.5.2<br>28.5.3                                               | k Diagram  Basic Configuration  EHCI Controller  OHCI Controller  ster Map  ctional Description  Initialization  Root Hub Port Routing Logic  OHCI                                     |                   |

| 28 | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund<br>28.5.1<br>28.5.2                                                         | wiew                                                                                                                                                                                   |                   |

| 28 | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund<br>28.5.1<br>28.5.2<br>28.5.3<br>28.5.4                                     | k Diagram  Basic Configuration  EHCI Controller  OHCI Controller  ster Map  ctional Description  Initialization  Root Hub Port Routing Logic  OHCI                                     |                   |

|    | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund<br>28.5.1<br>28.5.2<br>28.5.3<br>28.5.4                                     | k Diagram  Basic Configuration  EHCI Controller  OHCI Controller  ster Map  ctional Description  Initialization  Root Hub Port Routing Logic  OHCI  EHCI                               |                   |

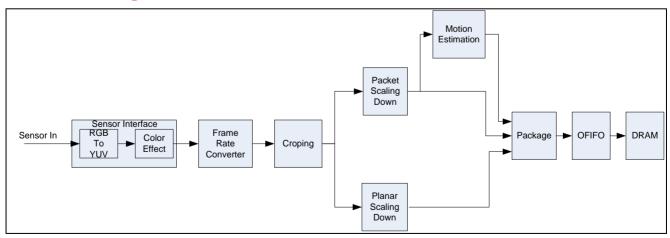

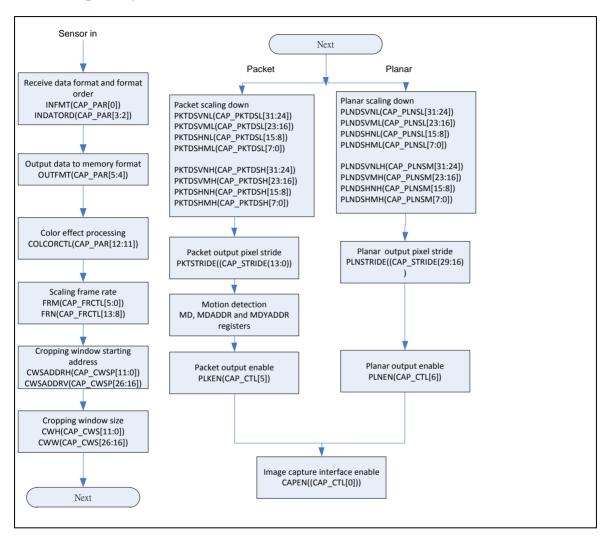

|    | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund<br>28.5.1<br>28.5.2<br>28.5.3<br>28.5.4<br>CAPTU<br>29.1 Over               | k Diagram  Basic Configuration EHCI Controller OHCI Controller  ster Map  ctional Description  Initialization Root Hub Port Routing Logic OHCI EHCI  SHORI SENSOR INTERFACE CONTROLLER |                   |

|    | 28.1 Over<br>28.2 Feato<br>28.3 Bloc<br>28.3.1<br>28.3.2<br>28.3.3<br>28.4 Regi<br>28.5 Fund<br>28.5.1<br>28.5.2<br>28.5.3<br>28.5.4<br>CAPTU<br>29.1 Over<br>29.2 Feato | wiew                                                                                                                                                                                   |                   |

| 29.5 Func  | tional Description                 | 303 |

|------------|------------------------------------|-----|

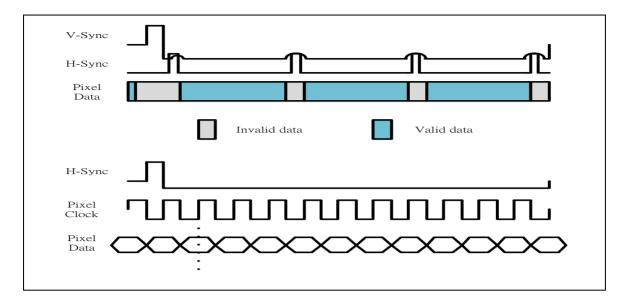

| 29.5.1     | Basic Configuration                |     |

| 29.5.2     | Image Capture Flow Chart           |     |

| 29.5.3     | Polarity and Input Data Order      |     |

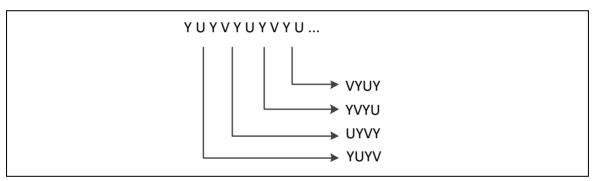

| 29.5.4     | Sensor Data Input Order            |     |

| 29.5.5     | Input and Output Data Format       |     |

| 29.5.6     | Downscale Factor                   |     |

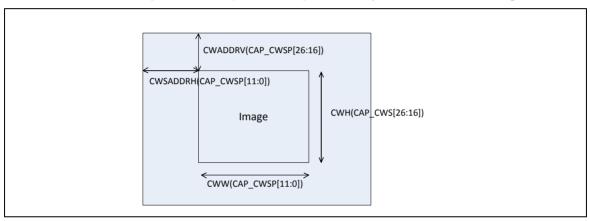

| 29.5.7     | Cropping Window and Start Position |     |

| 29.5.8     | One Shutter Mode (Single Frame)    |     |

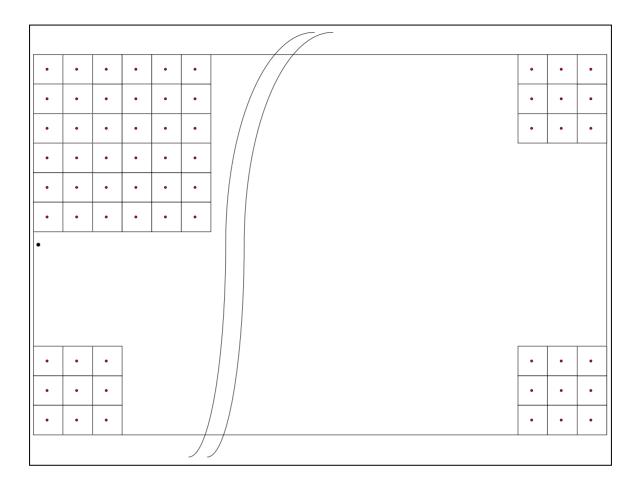

| 29.5.9     | Motion detection                   | 306 |

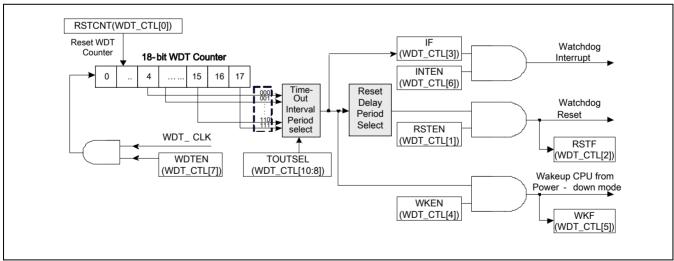

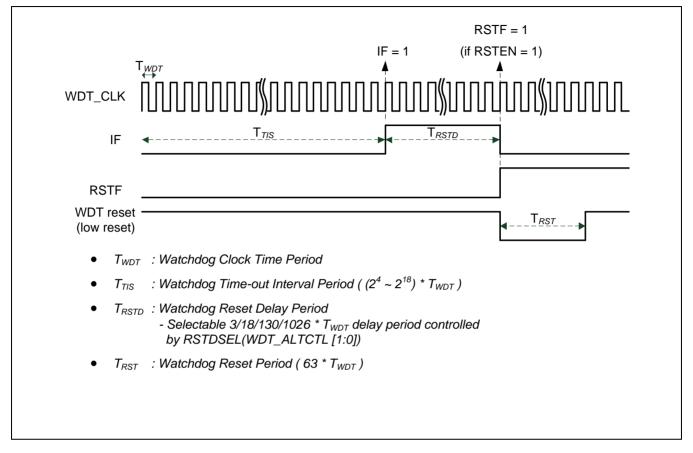

| 30 WATC    | HDOG TIMER (WDT)                   | 308 |

| 30.1 Over  | view                               | 308 |

| 30.2 Featu | ures                               | 308 |

| 30.3 Bloc  | k Diagram                          | 308 |

| 30.4 Regis | ster Map                           | 308 |

| 30.5 Func  | tional Description                 | 309 |

| 30.5.1     | WDT Configuration                  |     |

| 30.5.2     | WDT Wakeup                         | 310 |

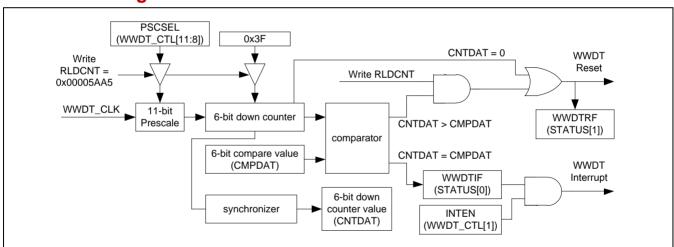

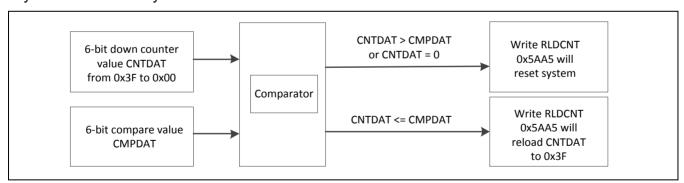

| 31 WINDO   | OW WATCHDOG TIMER (WWDT)           | 311 |

| 31.1 Over  | view                               | 311 |

| 31.2 Featu | ures                               | 311 |

| 31.3 Block | k Diagram                          | 311 |

| 31.4 Regis | ster Map                           | 311 |

| 31.5 Func  | tion Description                   | 312 |

| 31.5.1     | Timeout Setting                    | 312 |

| 31.5.2     | WWDT Interrupt                     | 313 |

| 31.5.3     | System Reset                       |     |

| 31.5.4     | WWDT Window Setting Limitations    | 313 |

|            |                                    |     |

# 1 System Manager

### 1.1 Overview

The system management describes following information and functions.

- System Resets

- System Memory Map

- System management registers for Product Identifier (PDID), Power-On Setting, System

Wake-Up, Reset Control for on-chip controllers/peripherals, and multi-function pin control.

- System Control registers

### 1.2 Register Map

R: read only, W: write only, R/W: both read and write

| Register          | Offset       | R/W | Description                                        | Reset Value                |

|-------------------|--------------|-----|----------------------------------------------------|----------------------------|

| SYS_BA = 0xB000_0 | 0000         | •   |                                                    |                            |

| SYS_PDID          | SYS_BA+0x000 | R   | Product Identifier Register                        | 0x0X30_D008 <sup>[1]</sup> |

| SYS_PWRON         | SYS_BA+0x004 | R/W | Power-On Setting Register                          | Undefined <sup>[2]</sup>   |

| SYS_ARBCON        | SYS_BA+0x008 | R/W | Arbitration Control Register                       | 0x0000_0000                |

| SYS_LVRDCR        | SYS_BA+0x020 | R/W | Low Voltage Reset & Detect Control Register        | 0x0000_0001                |

| SYS_MISCFCR       | SYS_BA+0x030 | R/W | Miscellaneous Function Control Register            | 0x0000_0200                |

| SYS_MISCIER       | SYS_BA+0x040 | R/W | Miscellaneous Interrupt Enable Register            | 0x0000_0000                |

| SYS_MISCISR       | SYS_BA+0x044 | R/W | Miscellaneous Interrupt Status Register            | 0x0001_0000                |

| SYS_WKUPSER       | SYS_BA+0x058 | R/W | System Wakeup Source Enable Register               | 0x0000_0000                |

| SYS_WKUPSSR       | SYS_BA+0x05C | R/W | System Wakeup Source Status Register               | 0x0000_0000                |

| SYS_AHBIPRST      | SYS_BA+0x060 | R/W | AHB IP Reset Control Register                      | 0x0000_0000                |

| SYS_APBIPRST0     | SYS_BA_0x064 | R/W | APB IP Reset Control Register 0                    | 0x0000_0000                |

| SYS_APBIPRST1     | SYS_BA_0x068 | R/W | APB IP Reset Control Register 1                    | 0x0000_0000                |

| SYS_RSTSTS        | SYS_BA_0x06C | R/W | Reset Source Active Status Register                | 0x0000_0007                |

| SYS_GPA_MFPL      | SYS_BA+0x070 | R/W | GPIOA Low Byte Multiple Function Control Register  | 0x0000_0000                |

| SYS_GPA_MFPH      | SYS_BA+0x074 | R/W | GPIOA High Byte Multiple Function Control Register | 0x0000_0000                |

| SYS_GPB_MFPL      | SYS_BA+0x078 | R/W | GPIOB Low Byte Multiple Function Control Register  | 0x0000_0000                |

| SYS_GPB_MFPH      | SYS_BA+0x07C | R/W | GPIOB High Byte Multiple Function Control Register | 0x0000_0000                |

| SYS_BA+0x080 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOC Low Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS_BA+0x084 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOC High Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x088 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOD Low Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x08C | R/W                                                                                                                                                                                                                                                                                                                              | GPIOD High Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x090 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOE Low Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x094 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOE High Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x098 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOF Low Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x09C | R/W                                                                                                                                                                                                                                                                                                                              | GPIOF High Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYS_BA+0x0A0 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOG Low Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

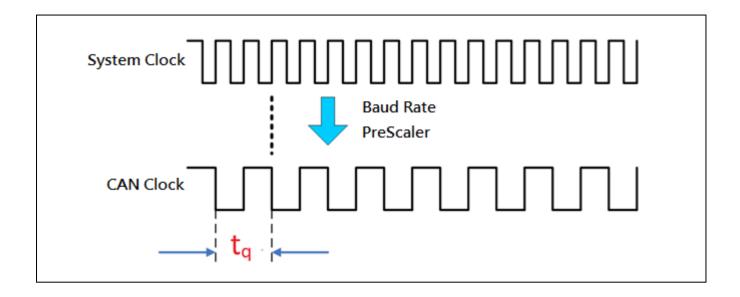

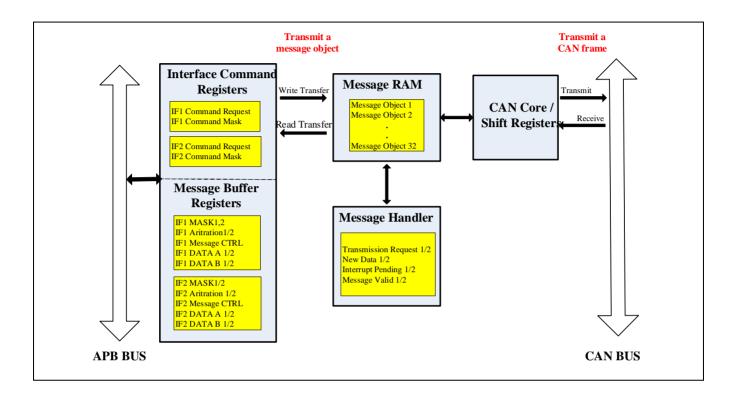

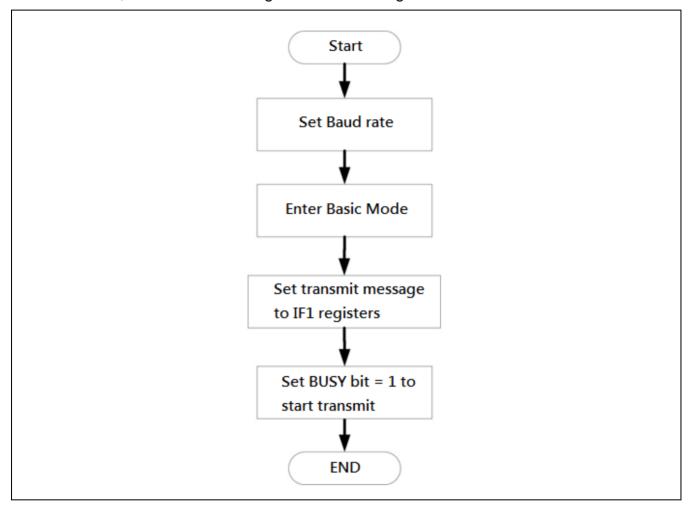

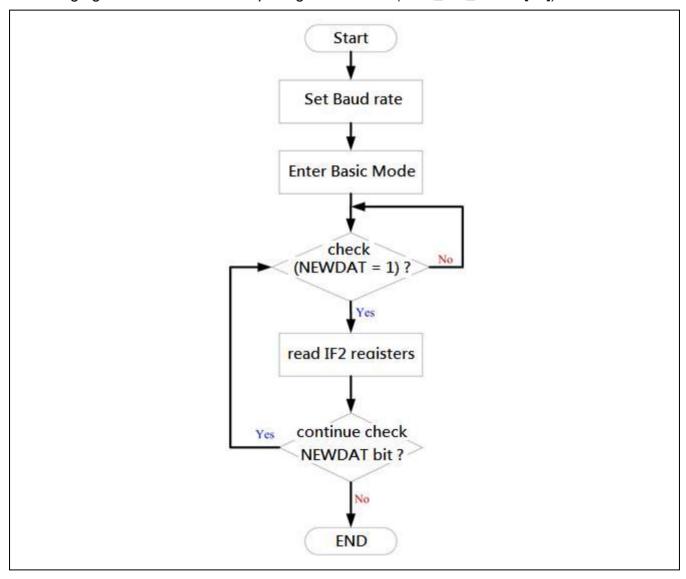

| SYS_BA+0x0A4 | R/W                                                                                                                                                                                                                                                                                                                              | GPIOG High Byte Multiple Function Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |