# Power MOSFET Maximum Ratings

# Outline

This document explains absolute maximum ratings, thermal resistance and safe operating area (SOA) of power MOSFETs.

# **Table of Contents**

| Outline                                                                             | 1  |

|-------------------------------------------------------------------------------------|----|

| Table of Contents                                                                   | 2  |

| 1. Absolute Maximum Ratings                                                         | 3  |

| 1.1. Definition                                                                     | 3  |

| 1.2. Parameters Specified as Absolute Maximum Ratings                               | 3  |

| 1.2.1. Drain-source voltage (V <sub>DSS</sub> )                                     | 3  |

| 1.2.2. Gate-source voltage (V <sub>GSS</sub> )                                      | 4  |

| 1.2.3. Drain current (I <sub>D</sub> )                                              | 4  |

| 1.2.4. Power dissipation ( $P_D$ )                                                  | 4  |

| 1.2.5. Avalanche current (I <sub>AS</sub> ) and avalanche energy (E <sub>AS</sub> ) | 5  |

| 1.2.6. Channel temperature ( $T_{ch}$ ) and storage temperature ( $T_{stg}$ )       | 7  |

| 1.2.7. Isolation voltage (V <sub>ISO(RMS)</sub> )                                   | 7  |

| 1.2.8. Tightening torque (TOR)                                                      | 7  |

| 2. Thermal Resistance                                                               | 8  |

| 2.1. What Is Thermal Resistance?                                                    | 8  |

| 2.2. Thermal Resistance Calculation                                                 | 8  |

| 2.3. Transient Thermal Impedance and Steady-State Thermal Resistances               | 9  |

| 3. Safe Operating Area (SOA)                                                        | 10 |

| 3.1. Forward-Bias Safe Operating Area                                               | 10 |

| 3.2. Restrictions of a Safe Operating Area                                          | 10 |

| RESTRICTIONS ON PRODUCT USE                                                         | 11 |

### 1. Absolute Maximum Ratings

#### 1.1. Definition

For power MOSFETs, the maximum allowable current, voltage, power dissipation and other characteristics are specified as maximum ratings.

In circuit design, understanding maximum ratings is very important in order to obtain the best performance from power MOSFETs and maintain device reliability throughout the target operating life.

Maximum ratings must not be exceeded in order to guarantee the lifespan and reliability of devices. For power MOSFETs, maximum ratings are defined using an absolute maximum rating system. Maximum ratings are the highest absolute values that must not be exceeded even instantaneously under any conditions.

A device may not be able to recover from stress that exceeds a specified maximum rating. None of the absolute maximum ratings may be exceeded. Care should therefore be exercised regarding bounces in supply voltage, variations in the characteristics of electronic devices, possible exposure to stress higher than maximum ratings during circuit adjustment, changes in ambient temperature, fluctuations in the input signal, and other such factors.

For example, power MOSFETs are rated in terms of drain current, pin-to-pin voltage, power dissipation, channel temperature, and storage temperature. These characteristics are interrelated and cannot be considered separately. They also depend on external circuit conditions.

| Characteristic                 |       | Symbol           | Unit | Description                                                                                                                     |

|--------------------------------|-------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------|

| Drain-source voltage           |       | V <sub>DSS</sub> | V    | The maximum voltage that can be applied across drain and source, with gate and source short-circuited                           |

| Gate-source voltage            |       | V <sub>GSS</sub> | V    | The maximum voltage that can be applied across gate and source, with drain and source short-circuited                           |

| Drain<br>current               | DC    | Ι <sub>D</sub>   | А    | The maximum DC current that can pass through the drain to source                                                                |

|                                | Pulse | I <sub>DP</sub>  |      | The maximum allowable peak drain current for pulsed operation                                                                   |

| Power dissipation<br>(Tc=25°C) |       | PD               | W    | The maximum power that can be dissipated by a MOSFET                                                                            |

| Avalanche current              |       | I <sub>AS</sub>  | А    | The maximum peak non-repetitive current that is permitted under avalanche conditions                                            |

| Avalanche energy               |       | E <sub>AS</sub>  | mJ   | The maximum non-repetitive energy that the MOSFET can dissipate under avalanche breakdown conditions                            |

| Channel temperature            |       | T <sub>ch</sub>  | °C   | The maximum allowable chip temperature at which a MOSFET operates                                                               |

| Storage temperature range      |       | T <sub>stg</sub> | °C   | The maximum temperature at which a MOSFET may be stored without voltage applying                                                |

| Isolation voltage              |       | VISO(RMS)        | V    | The maximum voltage at which a MOSFET can maintain<br>isolation between the designated point on the case and electrode<br>leads |

| Tightening torque              |       | TOR              | N∙m  | The maximum torque that may be applied in the axial direction when tightening a screw                                           |

#### 1.2. Parameters Specified as Absolute Maximum Ratings

(The specified characteristics differ from product to product. Ta=25°C unless otherwise specified.)

#### 1.2.1. Drain-source voltage (V<sub>DSS</sub>)

The drain-source breakdown voltages of a power MOSFET are defined as follows according to the gate-source bias conditions:

- (1) V<sub>DSS</sub>: Drain-source voltage with gate and source short-circuited. Applying a voltage higher than the rated value may cause a MOSFET to enter the breakdown region and be permanently damaged.

- (2) V<sub>DSX</sub>: Drain-source voltage with gate and source reverse-biased

In addition to  $V_{DSS}$  and  $V_{DSX}$ ,  $V_{DSR}$  and  $V_{DSO}$  are defined for power MOSFETs. ( $V_{DSR}$  is the drain-source voltage with a resistor inserted between gate and source.  $V_{DSO}$  is drain-source voltage with gate open-circuited.) Since power MOSFETs have very high input impedance, they should not be used in  $V_{DSO}$  mode. In this mode, power MOSFETs are biased between gate and source due to electrostatic induction and enter the conduction mode. Consequently, there is a high probability that they will be permanently damaged.

#### 1.2.2. Gate-source voltage (V<sub>GSS</sub>)

$V_{\rm GSS}$  is the maximum allowable gate-to-source voltage with drain and source short-circuited. This rating depends on the dielectric strength of the gate oxide. For MOSFETs, a permissible value is specified, taking practical voltage and reliability into consideration.

#### 1.2.3. Drain current (I<sub>D</sub>)

Generally, the maximum continuous (DC) current that the power MOSFET can pass in the forward direction is specified as  $I_D$ , whereas the pulsed current that the power MOSFET can pass in the forward direction is specified as  $I_{DP}$ . Likewise, the DC and pulsed currents in the reverse (diode) direction are specified as  $I_{DR}$  and  $I_{DRP}$ , respectively (under ideal heat dissipation conditions). However, the maximum current values in the forward direction are limited by the power loss caused by drain-source on-state resistance, and those in the reverse direction are limited by the power loss due to the forward voltage across the diode. Since current ratings are affected by heat dissipation conditions, maximum allowable current values are specified so that the channel temperature will not exceed the rated  $T_{ch}(max)$  value.

$$I_{D} = \sqrt{\frac{T_{ch}(max) - T_{c}}{R_{DS(on)}(max) \times R_{th(ch-c)}}}$$

$$I_{DP} = \sqrt{\frac{T_{ch}(max) - T_{c}}{R_{DS(on)}(max) \times r_{th(ch-c)}(t)}}$$

T<sub>ch</sub>(max): Maximum channel temperature

T<sub>c</sub>: Case temperature (25°C)

$R_{th(ch-c)}$ : Steady-state thermal resistance

rth(ch·c)(t): Transient thermal resistance

$R_{\mathrm{DS}(\mathrm{ON})}(\mathrm{max})$  : Maximum drain-source on-state resistance at the maximum channel temperature

The drain current  $I_D$  that the MOSFET device can carry is restricted not only by power loss but also by the current-carrying capability of a package, the maximum channel temperature, the safe operating area and other factors.

#### 1.2.4. Power dissipation (P<sub>D</sub>)

$P_{\text{D}}$  is the maximum power that the MOSFET can dissipate continuously under the specified thermal conditions.

The allowable power dissipation varies with the conditions under which the MOSFET is used (such as ambient temperature and heat dissipation conditions).

$P_D$  is calculated as the maximum power dissipation for a device with an infinite heat sink at 25°C ambient.

$$P_D = \frac{T_{ch}(max) - 25^{\circ}\text{C}}{R_{th(ch-c)}}$$

$P_{DP}$ , the maximum transient power dissipation, is calculated as follows using the transient thermal resistance value shown in individual MOSFET datasheets.

$$P_{DP} = \frac{T_{ch}(max) - 25^{\circ}\text{C}}{r_{th(ch-c)}(t)}$$

#### 1.2.5. Avalanche current (IAS) and avalanche energy (EAS)

When a power MOSFET operates at high speed as a switching device, a high surge voltage is applied across drain and source at the time of turn-off due to the self-inductance of a circuit and stray inductances. This surge voltage occasionally exceeds the rated voltage of the MOSFET, causing it to enter the breakdown region. At this time, avalanche current passes through the power MOSFET. Avalanche current exceeding the current or energy limit causes permanent damage to the MOSFET. This phenomenon is called avalanche breakdown. IAS is the maximum allowable avalanche current, and EAS is the maximum allowable avalanche energy.

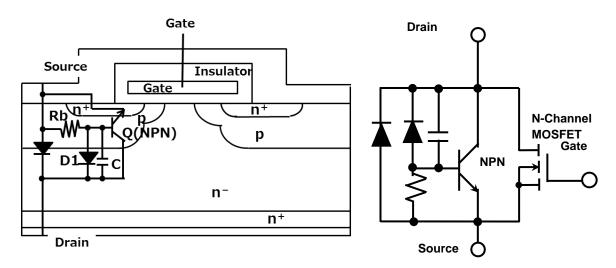

(1) MOSFET Equivalent Circuit

Figure 1.1 and Figure 1.2 show the cross section and equivalent circuit of a MOSFET.

# Figure 1.1 Cross Section of a MOSFET (Parasitic NPN Transistor)

(2) Avalanche operation

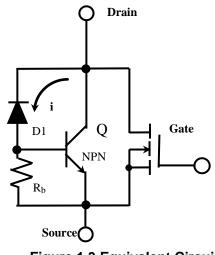

Avalanche operation Avalanche breakdown occurs in the following two modes. Figure 1.3 shows an equivalent circuit model for avalanche current.

Figure 1.2 MOSFET Equivalent Circuit

(a) Avalanche current breakdown

If a voltage higher than the withstand voltage is applied across drain and source, current i flows through resistor  $R_b$ . As a result, a forward voltage, i  $\times R_b$ , appears across the base and emitter of the transistor. If current i exceeds the permissible level, the parasitic NPN transistor turns on. When this happens, a large current flows through the transistor, resulting in the destruction of the device.

(b) Avalanche energy breakdown

If a voltage higher than the withstand voltage is applied across drain and source, current i flows. Because of this current and the applied voltage (i  $\times$  BV<sub>DSS</sub>), a power loss occurs. The resulting energy causes the device temperature to increase. The device is destroyed if it exceeds the rated channel temperature.

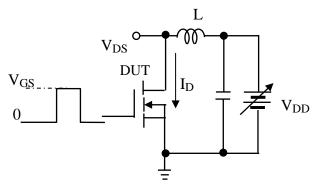

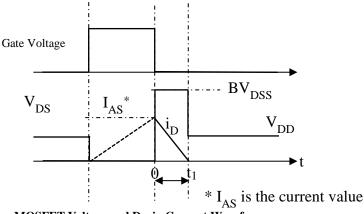

(3) Avalanche ruggedness and its measurement Figure 1.4 shows the test circuit for the avalanche capability of a power MOSFET. Figure 1.5 shows waveforms during avalanche breakdown. If the gate voltage  $V_{GS}$  drops below the threshold at turn-off, the drain current flowing through inductor L decreases, causing a sharp increase in drain-source voltage V<sub>DS</sub>. When VGS is higher than the threshold voltage, ID flows through the channel region of a power MOSFET. However, when VGs drops below the threshold voltage, the channel is shut off, causing ID to flow through the diode between drain and base (Figure 1.3). When this happens, V<sub>DS</sub> begins to increase. When it reaches the self-breakdown voltage, BV<sub>DSS</sub> (actual value), the power MOSFET experiences avalanche breakdown, and VDS levels off. The energy stored in L is transformed into heat,

Figure 1.3 Equivalent Circuit Model for Avalanche Current

causing a rise in device temperature. As a result,  $I_D$  drops to zero, and  $V_{DS}$  becomes equal to the supply voltage,  $V_{DD}$ . Avalanche current,  $I_{AS}$ , is the peak current allowed during avalanche breakdown. Avalanche energy,  $E_{AS}$ , is the maximum energy permissible at this time.

Figure 1.4 Typical Avalanche Test Circuit

**MOSFET Voltage and Drain Current Waveforms**

# Figure 1.5 Waveforms During Avalanche Breakdown

(4) Avalanche energy calculation Avalanche energy is calculated as follows:

From

$$\Delta V = -L \frac{di_D}{dt}$$

$BV_{DSS} - V_{DD} = -L \frac{di_D}{dt}$

$di_D = -\frac{BV_{DSS} - V_{DD}}{L} dt$

$i_D(t) = I_{AS} - \left(\frac{BV_{DSS} - V_{DD}}{L}\right) t$

$E_{AS} = \int_0^{t_1} i_D(t) \cdot BV_{DSS} dt$

$= \int_0^{t_1} \left\{ I_{AS} - \left(\frac{BV_{DSS} - V_{DD}}{L}\right) t \right\} \cdot BV_{DSS} dt$

$= \left[ I_{AS} BV_{DSS} t - \frac{1}{2} \left(\frac{BV_{DSS} - V_{DD}}{L}\right) BV_{DSS} t^2 \right]$

Substituting the following into  $t_1$ ,

$$\mathbf{t}_1 = \frac{I_{AS}L}{BV_{DSS} - V_{DD}}$$

and solving the equation gives:

$$E_{AS} = \frac{1}{2} L I_{AS}^2 \frac{B V_{DSS}}{B V_{DSS} - V_{DD}}$$

#### 1.2.6. Channel temperature ( $T_{ch}$ ) and storage temperature ( $T_{stg}$ )

The materials that constitute a power MOSFET and their reliability determine the maximum channel temperature  $T_{ch}(max)$ . The maximum channel temperature must be considered not only in terms of the functional operation of the power MOSFET, but also in terms of its reliability such as device degradation and lifetime.

Generally, degradation of the power MOSFET accelerates as the channel temperature increases. Let A and B be constants intrinsic to a transistor. Then, the average life in hours of operation  $L_m$  and the channel temperature in Kelvin (K)  $T_{ch}$  has the following relationship:

$$\log L_m = A + \frac{B}{T_{ch}}$$

Therefore, for power MOSFETs that must have a long-term guaranteed service life, the maximum channel temperature is determined, considering the defect rate and reliability requirements. Storage temperature  $T_{stg}$  is the temperature range in which a power MOSFET can be stored without voltage applying. The materials that constitute the power MOSFET and their reliability also determine the storage temperature range.

#### 1.2.7. Isolation voltage (VISO(RMS))

For devices housed in a fully molded package, isolation voltage represents the level of electrical isolation between the designated point on the case and the internal circuit and electrode terminals.  $V_{ISO(RMS)}$  is tested by applying AC voltage to the power MOSFET for a specified period of time. Isolation voltage is specified as the RMS of AC voltage.

#### 1.2.8. Tightening torque (TOR)

When attaching MOSFET devices to a thermal fin, the prescribed tightening torque must be followed. If the torque is too low, the mounting screws will loosen. If the torque is too high, the device could be damaged.

### 2. Thermal Resistance

#### 2.1. What Is Thermal Resistance?

Thermal resistance is the ability of a material to resist the flow of thermal energy.

The power consumed by a semiconductor chip is converted into heat, which is transferred to the case (package) and eventually released into ambient air through a thermal fin or other thermally conductive material. An increase in power dissipation ( $P_D$ ) causes a further increase in the device temperature ( $\Delta T$ ).

$\Delta T$  can be calculated as  $\Delta T = R_{th} \times P_D$ . Here,  $R_{th}$  is a constant defining a relationship between  $\Delta T$  and  $P_D$ . This constant is called thermal resistance.

#### 2.2. Thermal Resistance Calculation

The most commonly used thermal resistance values are:

$R_{th(ch-c)}$ : Channel-to-case thermal resistance

$$R_{th(ch-c)} = \frac{T_{ch}(max) - 25^{\circ}\text{C}}{P_D(T_c = 25^{\circ}\text{C})} \quad (^{\circ}\text{C}/W)$$

This is the thermal resistance of a device with an infinite heat sink when the case temperature is kept constant at an ambient temperature of 25°C.

Rth(ch-a): Channel-to-ambient thermal resistance

$$R_{th(ch-a)} = \frac{T_{ch}(max) - 25^{\circ}\text{C}}{P_D(T_a = 25^{\circ}\text{C})} \quad (^{\circ}\text{C}/W)$$

This is a thermal resistance from the channel to the ambient air at 25°C. It is equal to  $R_{th(ch-c)} + R_{th(c-a)}$ .

Note, however, that thermal resistance varies with board assembly condition and other factors.

#### 2.3. Transient Thermal Impedance and Steady-State Thermal Resistances

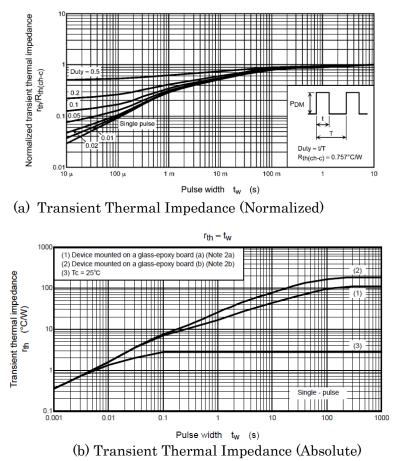

Transient thermal impedance is a function of time while the device is affected by thermal capacitance. It varies with the duty cycle of the pulse being applied.

Steady-state thermal resistance is a property during the time the device is no longer affected by thermal capacitance.

Figure 2.1 (a) and Figure 2.1 (b) show examples of transient thermal impedance curves as normalized and absolute values, respectively.

Figure 2.1. Transient Thermal Impedance Curves

# 3. Safe Operating Area (SOA)

#### 3.1. Forward-Bias Safe Operating Area

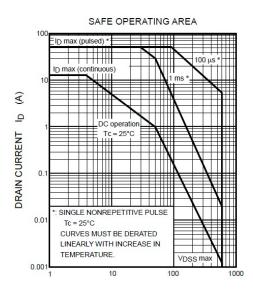

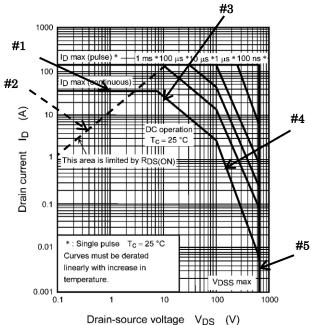

In a power MOSFET, current is not apt to concentrate in a small area. Therefore, unlike bipolar transistors, power MOSFETs are not generally vulnerable to secondary breakdown in a high voltage region.

However, as device geometries shrink, some power MOSFET devices have begun to exhibit a failure mode resembling secondary breakdown. As shown in Figure 3.1, the safe operating area SOA of such power MOSFETs is not limited by a line of a certain fixed power.

Figure 3.1 Example of an SOA with Varying Power Lines

#### 3.2. Restrictions of a Safe Operating Area

The safe operating area is limited by current, on-state resistance, heat, secondary breakdown and voltage as follows:

- 1. Current limit #1 defines the area limited by the drain current rating. For continuous-current (DC) operation, the SOA is constrained by IDmax. For pulsed operation, the SOA is bound by the I<sub>DP</sub>max line.

- 2. On-state resistance limit #2 defines the area that is theoretically constrained by the on-state resistance (R<sub>DS</sub>(ON)max). I<sub>D</sub> is equal to V<sub>DS</sub>/R<sub>DS</sub>(ON).

- 3. Thermal limit #3 is the area constrained by the power dissipation PD.

4. Limit imposed by secondary breakdown

$P_D$  (power dissipation) =  $I_D \times V_{DS}$

Figure 3.2 Safe Operating Area

With shrinking device geometries, some power MOSFETs have exhibited a failure mode resembling secondary breakdown in recent years. #4 represents the SOA bound by the secondary breakdown constraint.

5. Voltage limit #5 defines the area constrained by the drain-source voltage V<sub>DSS</sub>.

#### **RESTRICTIONS ON PRODUCT USE**

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications; (b) evaluating and determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. **TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.**

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.